## mipi<sup>®</sup> DEVCON

Ken Foust

A Developer's Guide to MIPI I3C<sup>SM</sup> for Sensors and Beyond

2017 MIPI ALLIANCE DEVELOPERS CONFERENCE

### Outline

- Introduction to MIPI I3C<sup>SM</sup>

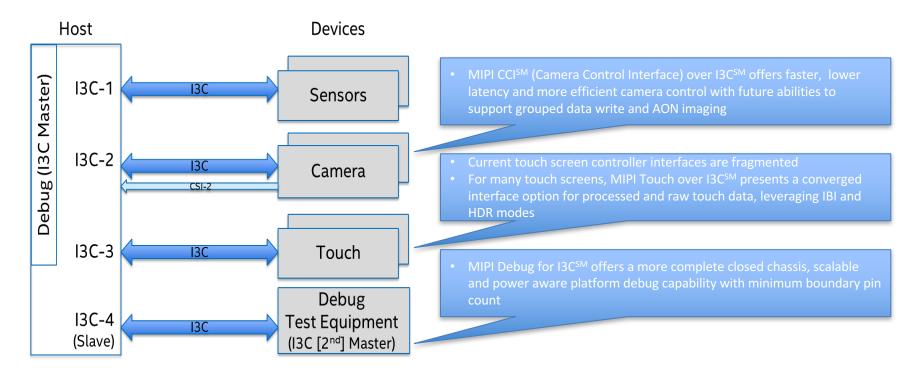

- Usages beyond sensing

- MIPI Camera Control Interface (CCI<sup>SM</sup>)

- MIPI Touch over I3C<sup>SM</sup>

- MIPI Debug for I3C<sup>SM</sup>

- MIPI I3C<sup>SM</sup> feature descriptions

- Implementation guidelines

- Legacy Device Support

- HDR Modes

- Varied Topologies

- Summarized good design practices

### **MIPI I3C<sup>SM</sup> for Ubiquitous Low Speed Interfacing**

- Anywhere sensors are used, MIPI I3C<sup>SM</sup> belongs

- Aimed toward historical I<sup>2</sup>C, SPI and UART applications in...

### What is MIPI I3C<sup>SM</sup>?

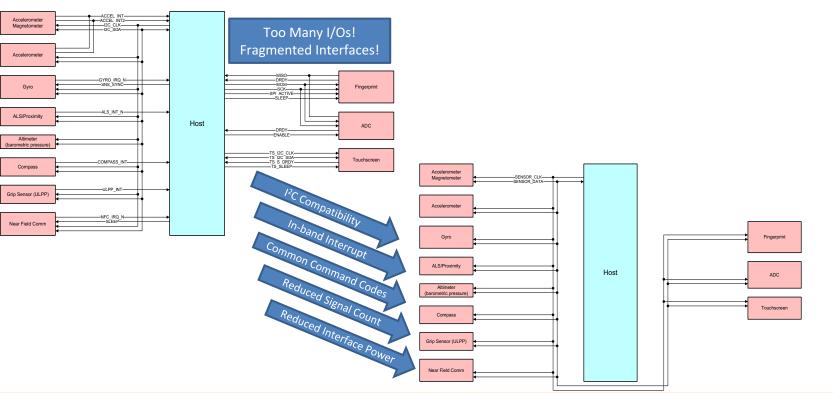

- Innovative new 2-Wire Sensor interface

- Key features address historical pain points

- In-band Interrupt, Dynamic Addressing, Multi-Master, Standardized Commands, Time Control, Hot-Join, Error Detection and Recovery

BANGALORE, INDIA | 2017

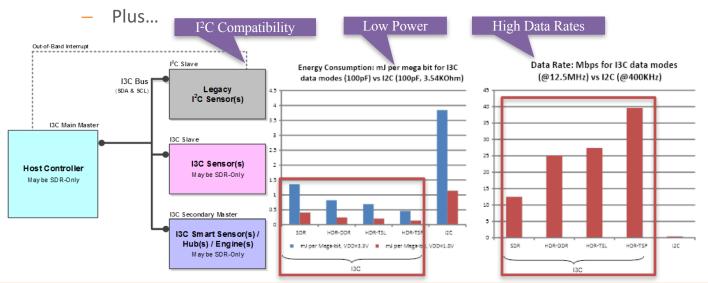

### MIPI I3C<sup>SM</sup> Vision?

### **Usages Beyond Sensing**

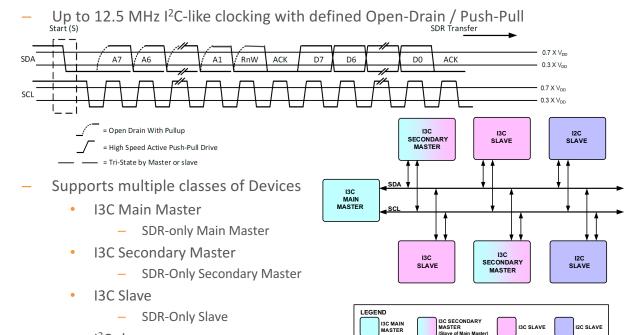

#### • I3C SDR – The Base Interface

I<sup>2</sup>C slave

- SDR Dynamic Address Assignment

- Standardized procedure for dynamic assignment of 7-bit Addresses to all I3C Devices

- I3C Slaves have two standardized characteristics registers and an internal 48bit Provisional ID to aide the procedure

- Legacy I<sup>2</sup>C Devices still use their static I<sup>2</sup>C Address

- SDR In-band Interrupt

- Slave device can issue START Request when in "Bus Available" state

- Master provides Interface Clock for Slave to drive it's Master-assigned address onto the bus

- Lowest assigned address wins arbitration in Open-Drain configuration

- A data payload (i.e. Mandatory Data Byte) can immediately accompany the In-band Interrupt

- Error Detection and Recovery Methodology

- For Master and Slave generated errors (9 Error Types identified, Parity, CRC5)

- Common Command Codes

- Standardized command mode with extensible set of MIPI-defined codes that can be Broadcasted and/or Directed, Read and/or Write

| S or Sr                                                                                                                     | 0x7E /                                                                                                                           | ' W / АСК | Command Code / T | Data (Optional) (Broadcast CCC only) / T | Sr or P |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------|------------------|------------------------------------------|---------|--|--|--|

| <ul> <li>Standardized Command Codes</li> <li>Event Enable/Disable</li> <li>Activity States</li> <li>Payload Mgmt</li> </ul> |                                                                                                                                  |           |                  |                                          |         |  |  |  |

|                                                                                                                             | <ul> <li>I3C Feature Mgmt (Dynamic Address Assignment, Mastership, HDR Modes,<br/>Timing Control)</li> <li>Test Modes</li> </ul> |           |                  |                                          |         |  |  |  |

|                                                                                                                             | Extensible Space (MIPI and Vendor)                                                                                               |           |                  |                                          |         |  |  |  |

### **Guidelines - Legacy I<sup>2</sup>C Device Support**

- Fm and Fm+ Speeds Supported

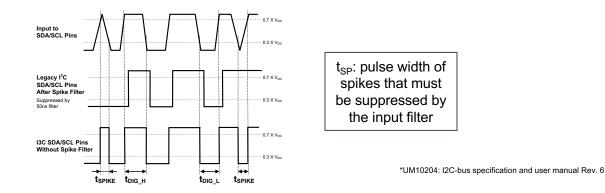

- 50ns Spike Filter (t<sub>SP</sub>) Needed for 12.5MHz I3C<sup>SM</sup> Clocking

- Clock Stretching is Not Allowed I3C SCL is Push/Pull

- 20mA Open Drain Drivers (I<sub>OI</sub>) are Not Used

- I<sup>2</sup>C Extended Addresses (10 bit) are Not Used

#### • I3C High Data Rate (HDR) Modes

- Optionally supported beyond the base SDR mode: 12.5MHz, SDA/SCL

- HDR-DDR: Double Data Rate

- HDR-TSL/TSP: Ternary Symbol

- Offer bit rates over 33Mbps at a fraction of the per bit power of I<sup>2</sup>C Fast Mode

- Simple Slave-side digital implementations

- Coexistent with legacy I<sup>2</sup>C Devices

- Leverage rising and falling edges

- Individually entered using broadcasted MIPI-defined Common Command Codes

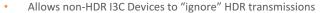

- Universally exited and restarted via MIPI-defined toggling patterns

#### • HDR-DDR: Double Data Rate

- Uses SCL as a clock, however Data and Commands change SDA on both SCL edges. By contrast, SDR Mode changes SDA only when SCL is Low

- HDR-DDR moves data by Words, which generally contains 2 preamble bits, 2 payload bytes and 2 parity bits. 4 Word Types defined: Command, Data, CRC, and Reserved

| SDA P1 P0 007 006 005 004 003 002 001 000 017 016 015 014 013 012 011 010 P1 P0                                                                                                                                                                                                        |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                                                                                                                        |  |

| Preamble Bits       Command, Data, or CRC       Parity Bits         Define the subsequent Word Types       Based on Preamble (2-bit MSB)       P1: Odd Parity bit       P0: Even Parity bit                                                                                            |  |

| — Simple protocol:                                                                                                                                                                                                                                                                     |  |

| HDR-DDR HDR Data<br>Command (1 or more words) HDR DDR HDR Exit P<br>HDR → ♦ <sdr></sdr>                                                                                                                                                                                                |  |

| From Master to Slave     ACK     = Acknowledge (SDA Low)       NACK     = Not Acknowledge (NACK)       From Slave to Master     S     = START Condition       Transition Bit     P     = STORT Condition       (Parity Bit for CCC)     T     = Transition Bit Alternative to ACKINACK |  |

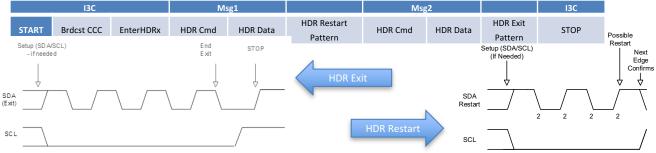

#### • HDR-TSL/TSP: Ternary Symbol Coding

- Ternary symbol coding for pure (TSP) and I<sup>2</sup>C legacy-inclusive (TSL) systems

- Given a two-wire interface with 'simultaneous' transitions and no traditional clock, there are 3 possible symbols available – 0, 1, 2

- Ideally, there are 3 possible "next" transition

- Transition indices are used to efficiently encode Binary into Ternary

- Simple protocol:

| I3C SDR |            |           | Msg1       |          |                           | Msg2    |          |                     | I3C  |

|---------|------------|-----------|------------|----------|---------------------------|---------|----------|---------------------|------|

| START   | Brdcst CCC | EnterHDRx | HDR<br>Cmd | HDR Data | HDR<br>Restart<br>Pattern | HDR Cmd | HDR Data | HDR Exit<br>Pattern | STOP |

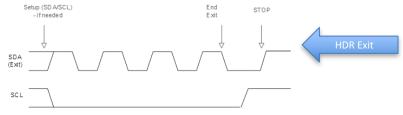

### **Guidelines - HDR Modes**

#### Enter HDR Commands Supported

|   | I3C  |            | Msg1      |         |          | Msg2                   |         |          | I3C                 |      |

|---|------|------------|-----------|---------|----------|------------------------|---------|----------|---------------------|------|

| S | TART | Brdcst CCC | EnterHDRx | HDR Cmd | HDR Data | HDR Restart<br>Pattern | HDR Cmd | HDR Data | HDR Exit<br>Pattern | STOP |

HDR Exit Pattern detected by all I3C Devices

Non-HDR Devices shall ignore I3C HDR bus traffic until the HDR Exit Pattern is detected

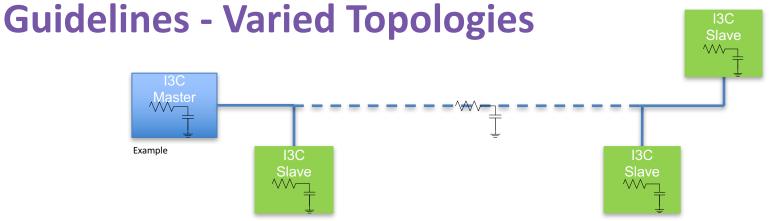

- Impacts on signal transition/transit times (maximum bus frequency)

- SDA/SCL drive strength: "weaker" for lower power and interference vs "stronger" for faster over larger topologies/loads

- Trace length and material: short vs long and pcb vs cable

- SCL/SDA pad capacitance

- Clock to Data Turnaround Time (t<sub>sco</sub>)

- Legacy I<sup>2</sup>C Devices impact maximum bus frequency (MHz)

- Must run I3C at speeds/pulses beyond Spike Filter or slow Bus to that of slowest I<sup>2</sup>C Device

- Impacts on signal integrity/reliability

- Device Location: close and far Devices can cause interference from reflections

### **Summarized Good Design Practices**

- Thoroughly understand capability of coexistent Legacy I<sup>2</sup>C Devices

- 50ns Spike Filter

- Disabled Clock Stretch

- Understand bus topology and performance tradeoffs Mixed (I3C and Legacy I<sup>2</sup>C Devices) vs Pure Bus (I3C Devices Only)

- Trace length and material

- SDA/SCL pad capacitance

- Clock to Data Turnaround Time (t<sub>sco</sub>)

- Device location

#### **Any Questions?**

# mipi DEVCON THANK YOU

BANGALORE, INDIA

2017 MIPI ALLIANCE DEVELOPERS CONFERENCE