# mipi<sup>®</sup> DEVCON

Mohamed Hafed Introspect Technology

MIPI C-PHY<sup>SM</sup> And How It Enables Next Generation Display and Camera Implementations

2017 MIPI ALLIANCE DEVELOPERS CONFERENCE

I HARD THERE IS AND THE THE OWNER THE THE TWO YES, INC.

US 8,472,551 B2

\*Jun. 25, 2013

(10) Patent No.:

(45) Date of Patent:

#### **Original Spark: Three Phase Encoding!**

#### FOREIGN PATENT DOCUMENTS (54) THREE PHASE AND POLARITY ENCODED SERIAL INTERFACE 1871635 A 11/2006 1207649 5/2002 2002199032 A 7/2002 WO2005041164 5/2005 (75) Inventor: George A Wiley, San Diego, CA (US) (73) Assignce: QUALCOMM Incorporated, San OTHER PUBLICATIONS International Source Report and Writen Opinion—PCTU82008 International Source Report and Writen Opinion—PCTU82008 Secarato J., "Multimedia messaging service for OPINS and UMTers-New 24, 2008. Secarato J., "Multimedia messaging service for OPINS and UMTers-Net To PCTURE Sec. 2009, pp. 112–11458, vol. 3 IEEE on PCTURE Sec. 2009, pp. 112–11458, vol. 3 Security J., Status P., Polyane D., Status Wei, High-Speel I.O. Links, "Produced Disasteriations and Theses, 2019, UCL-A. Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days. This patent is subject to a terminal dis-Japane P.O. Links, "Frequencies Dissociations and Fineses, 2016, CCLA, 189 pages, John Poulton, et al., "Multiwire Differential Signaling," UNC-CH Department of Computer Science, Version 1.1, Aug. 6, 2003. (21) Appl. No.: 13/301,454 (22) Filed: Nov. 21, 2011 (Continued) **Prior Publication Data** Primary Examiner — Shuwang Liu Assistant Examiner — James M Perez (74) Attorney: Agent, or Firm — Kevin T. Cheatham; US 2012/0155565 A1 Jun. 21, 2012 Related U.S. Application Data Raphael Freiwirth (63) Continuation of application No. 11/712,941, filed on Mar. 2, 2007, now Pat. No. 8,064,535. 1 Unit Interval of 2.285 Bits of (57) ABSTRACT A high speed serial interface is provided. In one aspect, the (51) Int. Cl. high speed serial interface uses three phase modulation for jointly encoding data and clock information. Accordingly, the H04L 25/34 H04L 25/49 (2006.01) (2006.01) need for de-skewing circuitry at the receiving end of the (52) U.S. CL USPC interface is eliminated, resulting in reduced link start-up time and improved link efficiency and power consumption. In one embodiment, the high speed serial interface uses fewer signal 375/288; 375/289; 375/292; 341/58; Information 341/69; 341/70 (58) Field of Classification Search conductors than conventional systems having separate con-ductors for data and clock information. In another embodi-ment, the serial interface allows for data to be transmitted at USPC .... 375/259-264, 284-288, 290-293; 341/50, 341/58, 68-70 See application file for complete search history. any speed without the receiving end having prior knowledge of the transmission data rate. In another aspect, the high speed serial interface uses polarity encoded three phase modulation (56) References Cited for jointly encoding data and clock information. This further U.S. PATENT DOCUMENTS for more than one bit to be transmitted in any single baud 5/1980 Ahamed 11/1993 Carlstedt 10/1994 Weddle et al. 4,201,958 A 5,259,002 interval (Continued) 39 Claims, 15 Drawing Sheets ~ 311

George Wiley, Qualcomm

(12) United States Patent

Wiles

Data

#### **Basic Concept – One Trio**

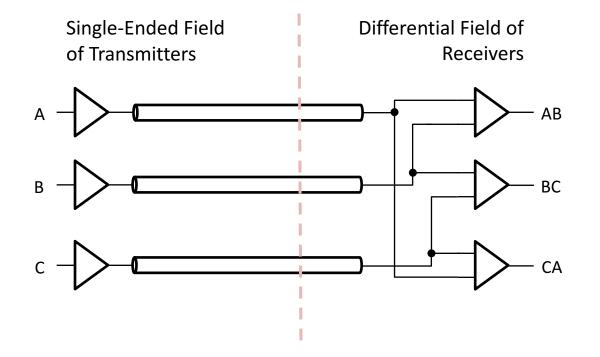

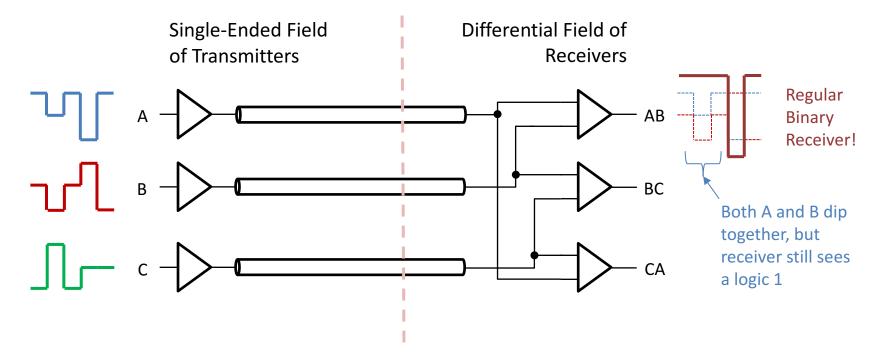

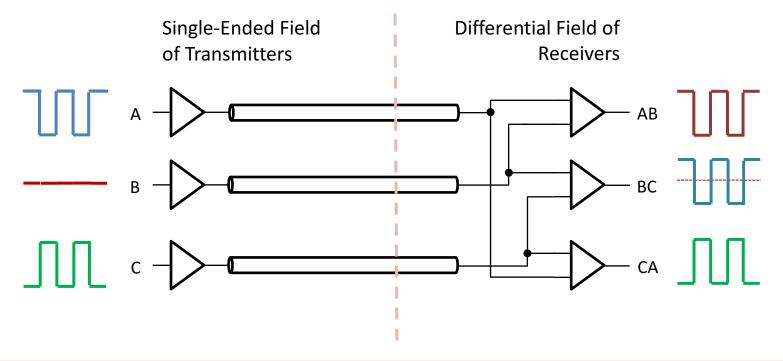

# Three Voltage Levels Ensure Proper Differential Reception

## **Key Takeaways**

Three-level single-ended signaling

Non-deterministic transitions based on self-clocked mapping and encoding algorithm

# **Encoding and Mapping**

#### **MIPI CPHY<sup>SM</sup> Data Types**

- 3 wires per lane

- 3-level wires (LOW, MID, HIGH)

- Every unit interval must contain LOW, MID, and HIGH wires

- No two consecutive identical states

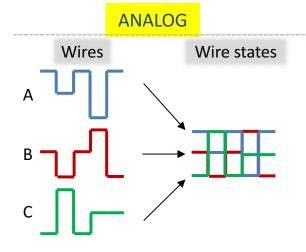

#### Wire States

- A wire state is the collection of A, B, and C

- 6 possible wire states

|      | ANALOG |      | DIGITAL<br>(3 bits) |     |     |                    |

|------|--------|------|---------------------|-----|-----|--------------------|

| Α    | В      | С    | A>B                 | B>C | C>A | Wire state<br>name |

| HIGH | LOW    | MID  | 1                   | 0   | 0   | +x                 |

| LOW  | HIGH   | MID  | 0                   | 1   | 1   | -x                 |

| MID  | HIGH   | LOW  | 0                   | 1   | 0   | +у                 |

| MID  | LOW    | HIGH | 1                   | 0   | 1   | -у                 |

| LOW  | MID    | HIGH | 0                   | 0   | 1   | +z                 |

| HIGH | MID    | LOW  | 1                   | 1   | 0   | -Z                 |

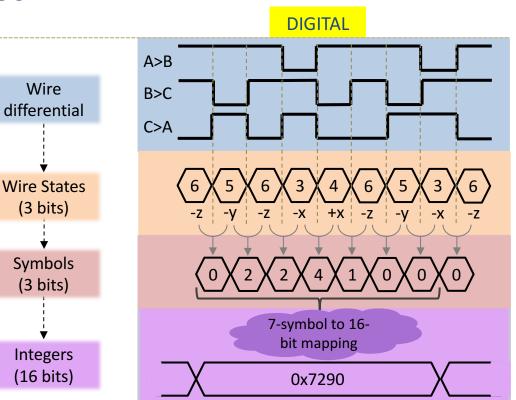

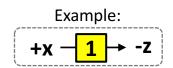

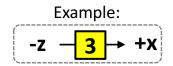

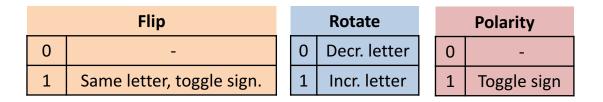

### Symbols: Now We're Transmitting!

- A symbol represents a transition between two wire states

- 5 possible symbols

|   | Symbol (3 bits) |        |          |  |

|---|-----------------|--------|----------|--|

|   | Flip            | Rotate | Polarity |  |

| 0 | 0               | 0      | 0        |  |

| 1 | 0               | 0      | 1        |  |

| 2 | 0               | 1      | 0        |  |

| 3 | 0               | 1      | 1        |  |

| 4 | 1               | DC     | DC       |  |

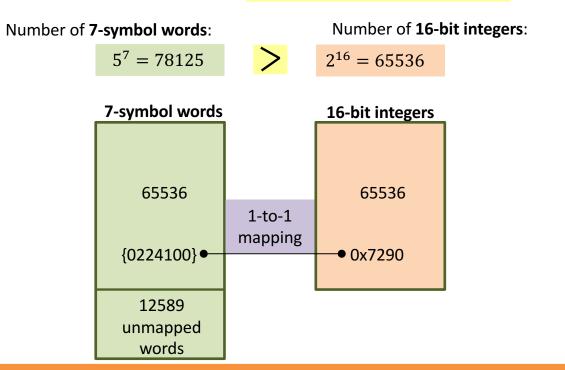

# Mapping 7 Symbols $\iff$ 16-bit Integers

• MIPI C-PHY<sup>SM</sup> defines a mapping between 7-symbol words and 16-bit integers

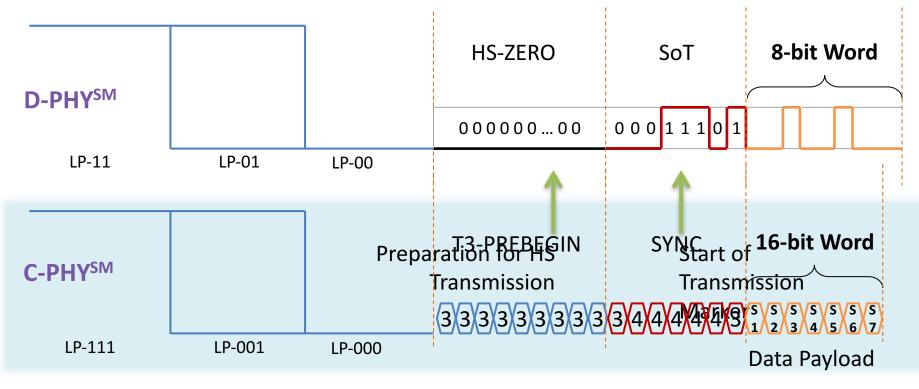

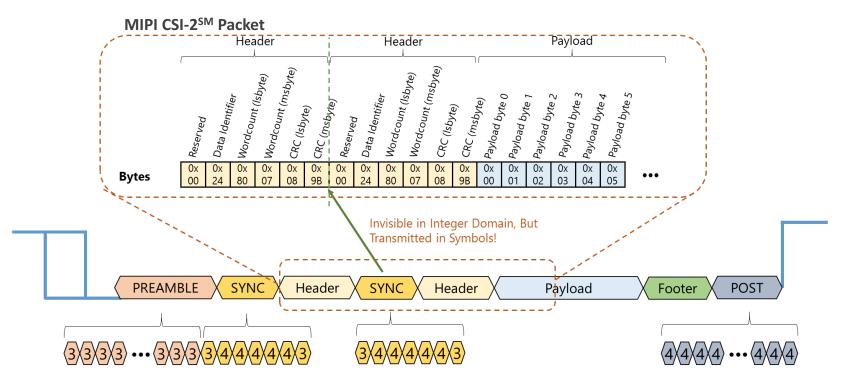

#### **Global Packet Transmission Similar to MIPI D-PHY<sup>SM</sup>**

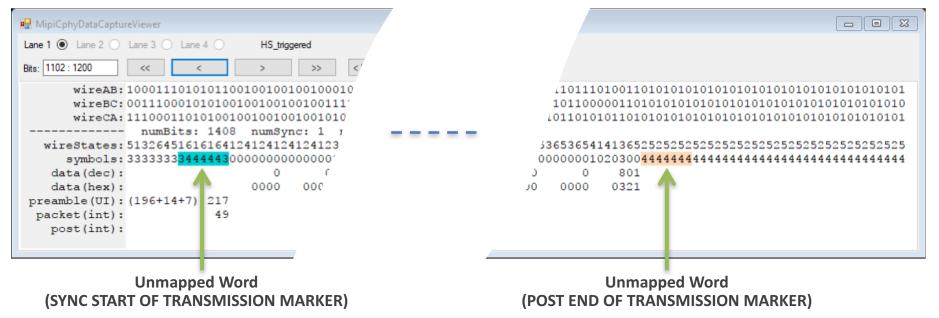

### **Tool View**

|                        | HipiCphyDataCaptureViewer                                                                            |                                                                 |

|------------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| Three-Phase<br>Signals | Lane 1 @ Lane 2 Lane 3 Lane 4<br>Bits: 3612:3701<br>wireAB: 0000000011100011100011100011100011100101 | 011001010111010110<br>1011100010101111011<br>123512425632531231 |

|                        | data(hex): 00A0 442A 901A                                                                            | 0E46 EBA8 A1                                                    |

**Decoded Data**

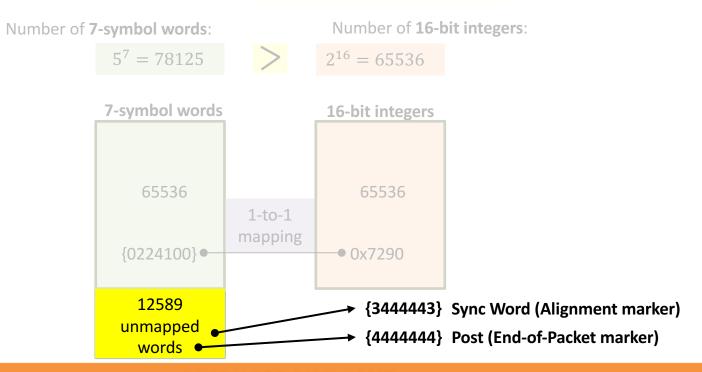

# MIPI C-PHY's Magical Unmapped Words!

### **MIPI C-PHY's Magical Unmapped Words!**

• MIPI C-PHY<sup>SM</sup> defines a mapping between 7-symbol words and 16-bit integers

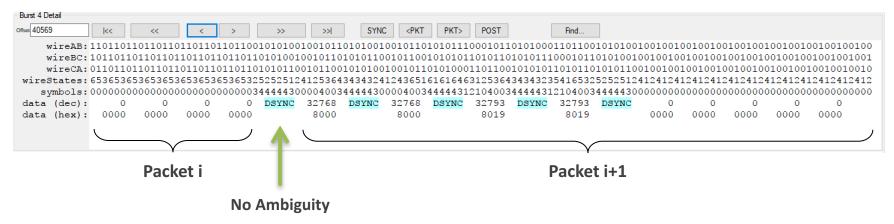

### **Easily Delineate Bursts... Really Easily!**

#### SYNC and POST

#### Send Unmapped Words Within HS Bursts!

| 🖳 MipiCphyDataCaptureViewer     |                                        |                                     |                            |                 |

|---------------------------------|----------------------------------------|-------------------------------------|----------------------------|-----------------|

| HS_immediate                    |                                        |                                     |                            |                 |

| ● lane1 ○ lane2 ○ lane3 ○ lane4 |                                        |                                     |                            |                 |

| Full Capture Packets            |                                        |                                     |                            |                 |

| Bits: 254 : 366 << >            | >>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>> | Find                                |                            |                 |

| wireAB: 0101011111101001003     | 101011100110101010101010101            | 1010000110111010100011011101        | 00101111100101010111000101 | 100101100010100 |

| wireBC: 0101010101010010010     | 01111001000101011101011011             | 0100111101010101011100010110        | 01011000101001010101101010 | 001011001001111 |

| wireCA: 101010001010010010      | 110000101010101000000010110            | )1101010001100101010110101000       | 10110010011110101000110111 | 010010111110010 |

| numBits: 7946688                | numSync: 821                           |                                     |                            |                 |

| wireStates: 1616164656524124123 | 53626452145252526242436530             | 55341232643564343432354165624       | 12536454613516161646312535 | 412436513152632 |

| symbols: 344444310204000004     | 40013334223444443102040000             | 00040013334223444443121040210       | 00400331143234444431210402 | 100040033114323 |

| data(dec): 32801 327            | 768 35581 <mark>None</mark> 32801      | 32768 35581 <mark>None</mark> 34841 | 32769 35679 None 34841     | 32769 35679     |

| data(hex): 8021 80              | 000 8AFD 8021                          | 8000 8AFD 8819                      | 8001 8B5F 8819             | 8001 8B5F       |

|                                 |                                        | •                                   |                            |                 |

|                                 | <b>A</b>                               |                                     | <b>A</b>                   |                 |

|                                 | T                                      | T                                   |                            |                 |

|                                 |                                        |                                     |                            |                 |

|                                 |                                        |                                     |                            |                 |

|                                 |                                        |                                     |                            |                 |

#### **Example: Packet Header Resynchronization**

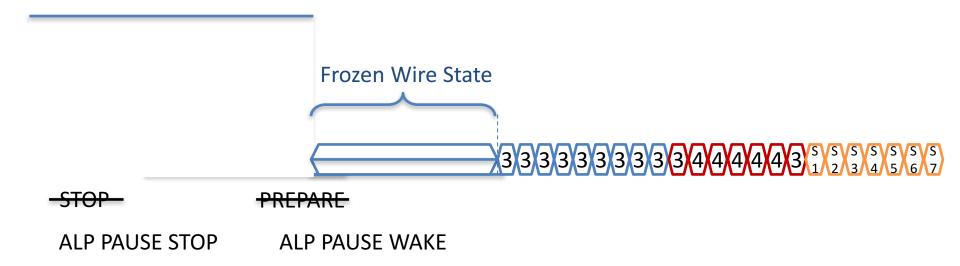

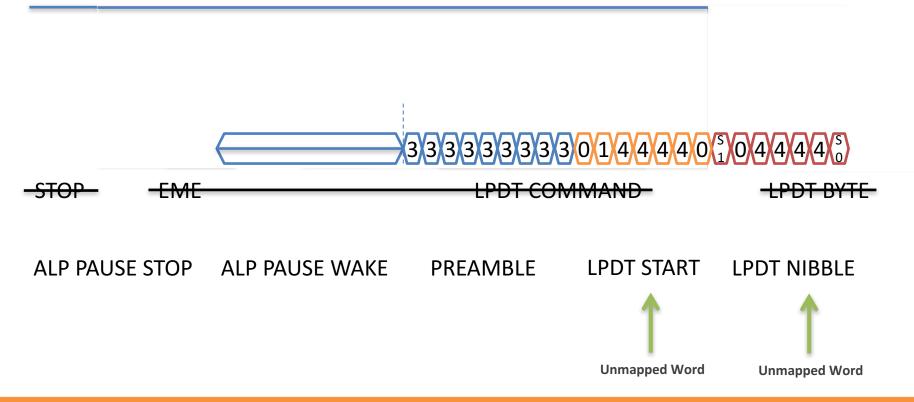

#### **Example: Alternate Low Power Mode**

#### **Example: Alternate Low Power Mode**

#### **Unmapped Words Enable a Wide Range of Codes**

| Symbol Sequence | ALP Function Code |

|-----------------|-------------------|

| 0244440         | Stop Code         |

| 0244441         | ULPS Code         |

| 0244442         | Trig 1 Code       |

|                 |                   |

| 444444          | Post2             |

Same functionality as legacy LP EME Sequences

# **Multiple SYNC Word Types**

# BANGALORE, INDIA

22

### **SYNC Is an Unmapped Word**

- Five (5) possible SYNC words exist

- 344440

- 3444441

- •••

- First SYNC word in a burst is always 3444443

- Multiple SYNC words used to trigger different seed types for MIPI CSI-2<sup>SM</sup> scrambling

# MIPI CSI-2<sup>SM</sup> Imaging Features Enabled by C-PHY

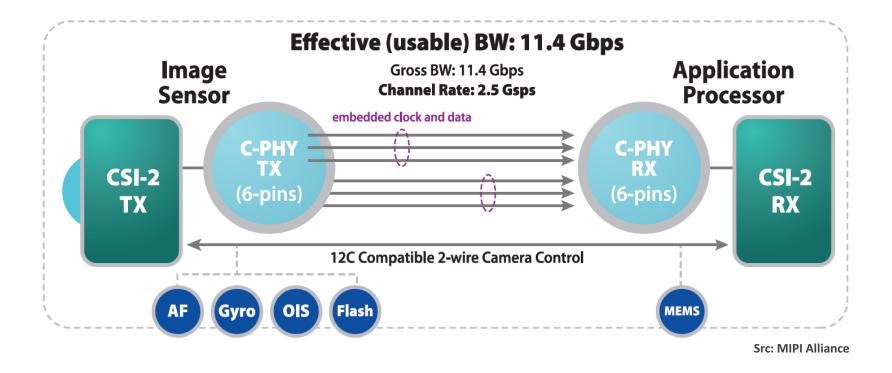

#### MIPI CSI-2<sup>SM</sup> Imaging Features Enabled by MIPI C-PHY<sup>SM</sup>

- Long Reach Transport Efficiency (LRTE)

- Easily delimits packets using **unmapped words**

- ALPS

- Helps maintain low voltage levels in advanced process nodes

- Up to 32 Virtual Channels

- Useful for imaging and vision applications supporting multiple sensor streams

#### MIPI CSI-2<sup>SM</sup> Imaging Features Enabled by MIPI C-PHY<sup>SM</sup>

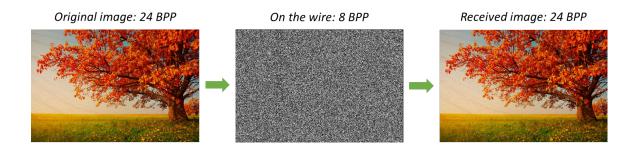

- Scrambling

- Provides a **wide range of seed** triggers using multiple SYNC words

- Future support for sensor fusion and camera commands

- MIPI C-PHY<sup>SM</sup> natively enables future technologies for more efficient camera commands than those using legacy LP mode

### MIPI DSI-2<sup>SM</sup> Protocol Features Enabled by MIPI C-PHY<sup>SM</sup>

### MIPI DSI-2<sup>SM</sup> Features Enabled by MIPI C-PHY<sup>SM</sup>

- Fast packets

- Unmapped words enable very robust packet delimiting within a burst

### MIPI DSI-2<sup>SM</sup> Features Enabled by MIPI C-PHY<sup>SM</sup>

- Display stream compression

- Complete compatibility with compression needs

### MIPI DSI-2<sup>SM</sup> Features Enabled by MIPI C-PHY<sup>SM</sup>

- MIPI Display Command Set (DCS<sup>SM</sup>) Mode

- Proven technology for buffered frame transmissions

- Scrambling

- Full support for scrambling at the protocol level

### Summary

MIPI C-PHY<sup>SM</sup> is based on a three-phase encoding scheme resulting in high transport efficiency over bandwidth-constrained channels

MIPI C-PHY<sup>SM</sup>'s unmapped words create extremely robust control, transmission, and messaging mechanisms at the protocol level

Next generation imaging (MIPI CSI-2<sup>SM</sup>), vision (MIPI CSI-2<sup>SM</sup>), and projection (MIPI DSI-2<sup>SM</sup>) applications can benefit greatly from MIPI C-PHY<sup>SM</sup>'s powerful protocol features

# mipi DEVCON THANK YOU

BANGALORE, INDIA

2017 MIPI ALLIANCE DEVELOPERS CONFERENCE