# mipi<sup>®</sup> DEVCON

Sanjeev Kumar, Lead Engineer, Sr Qualcomm India Private Limited

Purva Joshi, Engineer Qualcomm India Private Limited

Ritesh Jain, Engineer, Sr Staff/Manager Qualcomm India Private Limited

MIPI-SPMI<sup>SM</sup> 1.0 Multi-master Verification

# BANGALORE, INDIA

2017 MIPI ALLIANCE DEVELOPERS CONFERENCE

## Agenda

- MIPI-SPMI An Introduction

- MIPI-SPMI Multi-master Verification Architecture

- Verification Challenges and their Solutions

- Conclusions and References

## **MIPI-SPMI – An Introduction**

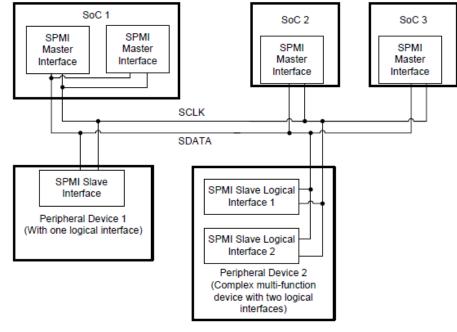

- SPMI (System Power Management Interface):

- 2-wire serial interface

- Supports up-to 4 masters and 16 slaves

- Connects the integrated Power Controller (PC) of a System-on-Chip (SoC) processor system with one or more Power Management Integrated Circuits (PMIC) voltage regulation systems

- Within PC, SPMI-related functions are referred to as "Master".

- Within PMIC, SPMI related functions are referred to as "Slave".

## **MIPI-SPMI – An Introduction**

Figure 1 SPMI System Example Qualcomm India Private Limited

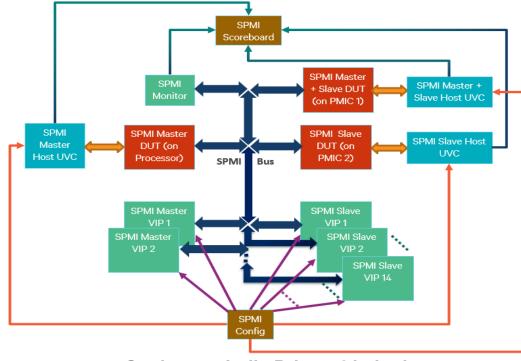

## **MIPI-SPMI Multi-master Verification Architecture**

**Qualcomm India Private Limited**

# **Verification Challenges and their Solutions**

- Multiple masters waking up at the same time and trying to connect

- No RCS request

- Pending RCS request

- Second master trying to connect when one master is already present

- SSC Detection

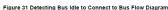

- Bus Idle

- Bus Arbitration

- Multiple masters and slaves arbitrating with different priority levels

- A-bit and SR-bit for slaves; priority and secondary MPLs for masters

# **Verification Challenges and their Solutions**

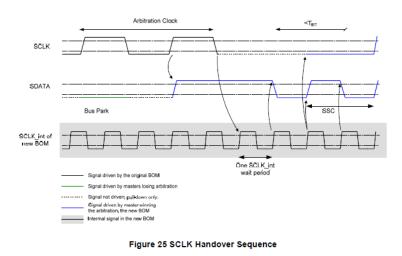

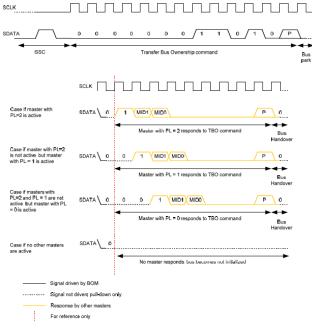

- BOM (Bus Owner Master) transfer, i.e. SCLK Handover

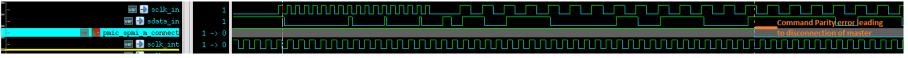

- Disconnection of a master

- Using TBO command

- During command parity error

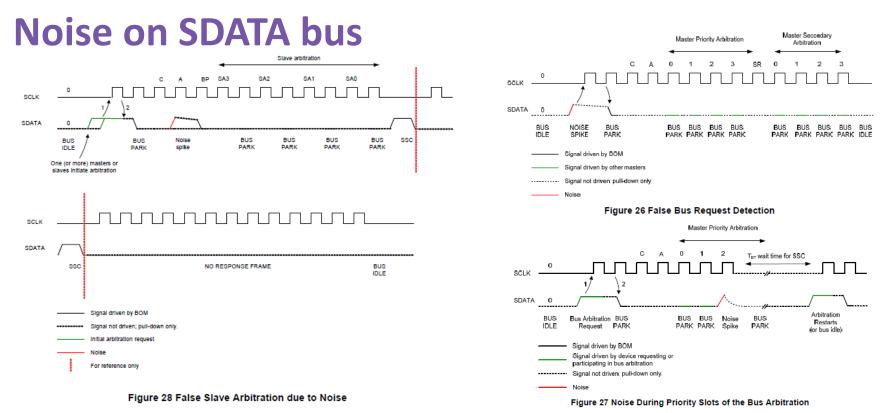

- Noise during

- Bus Idle

- Master Arbitration

- Slave Arbitration

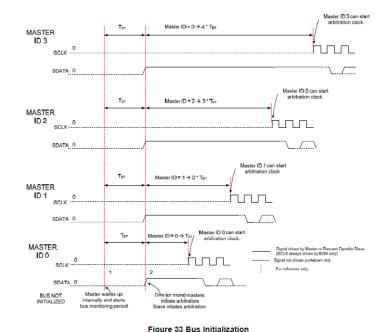

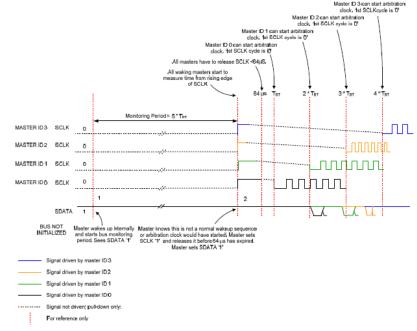

# Multiple masters waking up at the same time and trying to connect

Figure 34 Bus Initialization with Pending Bus Arbitration Request by RCS

**Qualcomm India Private Limited**

## Second master trying to connect when one master is

### already present

Note: This procedure runs simultaneously with the Detecting Bus Idle procedure

Figure 30 Detecting SSC to Connect to Bus Flow Diagram

**Qualcomm India Private Limited**

Figure 32 Detecting Bus Arbitration to Connect to Bus Flow Diagram

# Multiple masters and slaves arbitrating with different priority levels and BOM (Bus Owner Master) transfer

**Qualcomm India Private Limited**

## **Disconnection of a master**

Figure 46 Transfer Bus Ownership Command Sequence

**Qualcomm India Private Limited**

**Qualcomm India Private Limited**

## **Conclusions and References**

- MIPI-SPMI protocol plays a vital role in reducing the number of pin connections in a chipset as it support multi-master and multi-slave systems and various types of data path commands.

- There are certain areas which needs some improvement. Some of them has been addressed in MIPI-SPMI spec ver. 2.0. Some more are yet to be taken care as suggested by us in this presentation.

- Reference: MIPI<sup>®</sup> Alliance Specification for System Power Management Interface (SPMI) - Version 1.0 – 27 October 2008

# mipi DEVCON THANK YOU

BANGALORE, INDIA

2017 MIPI ALLIANCE DEVELOPERS CONFERENCE