**SK Choi**Keysight Technologies

Next Generation MIPI Physical Layer Design and Evaluation Challenges

2017

MIPI ALLIANCE

DEVELOPERS

CONFERENCE

BANGALORE, INDIA

MIPI.ORG/DEVCON

## Agenda

- New specification and CTS changes in 2017

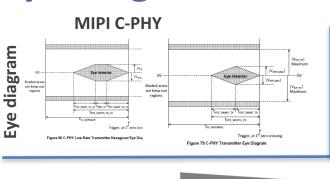

- Eye diagram tests changes and challenges

- MIPI C-PHY<sup>SM</sup>

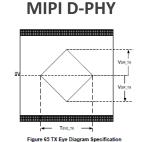

- MIPI D-PHY<sup>SM</sup>

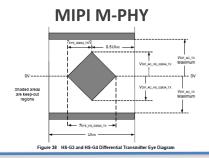

- MIPI M-PHY<sup>®</sup>

- SSC test

- MIPI D-PHY<sup>SM</sup>

# **Specification updates in MIPI C-PHY**

C-PHY 1.1: Approved Feb 11, 2016

C-PHY 1.2: Approved Mar 28, 2017

- RCLK jitter(reference clock jitter) Annex to chapter 9

- Receiver calibration removing PVT(Process, Voltage and Temperature variation after Long LP signal)

#### **CTS updates in MIPI C-PHY**

CTS 1.0 : Approved Feb 12, 2016

CTS 1.1: expected approve Aug, 2017

- Test 1.2.21 Tx Eye Pattern Test

- Test 1.4.1 HS-TX Differential Voltages

Unterminated

- Test 1.4.2 HS-TX Differential Voltage

Mismatch Unterminated

- Test 1.4.3 HS-TX Single-Ended Output High Voltages Unterminated

- Test 1.4.4 HS-TX Static Common-Point Voltages Unterminated

#### **Specification updates in MIPI D-PHY**

D-PHY 2.0: Approved Mar 8, 2016

D-PHY 2.1: Approved Mar 28, 2017

- Lower LP voltage level from 1.2V to 1V

- HS-Idle (lower latency)

- Programmable Preamble(RX PVT calibration due to LP signal)

## **CTS updates in MIPI D-PHY**

CTS 1.2: April 24, 2017

CTS v2.0/v2.1

- Test 1.5.7 HS-TX Eye Diagram

- Test 1.4.19 TX Spread Spectrum Clocking(SSC) Requirement

- ZID open case test

- Direct connection supporting in HS continuous mode.

CTS 2.0/2.1: expected finished in October

## **Specification updates in MIPI M-PHY**

M-PHY 4.0 : Approved Aug 3, 2015

- Minor spec clarification

- Target BER 10<sup>-10</sup> to 10<sup>-12</sup>

M-PHY 4. 2.1: Approved Mar 28, 2017

#### **CTS updates in MIPI M-PHY**

CTS 3.1 : On-going(revision 21)

CTS 4.0/4.1: On-going(revision 1)

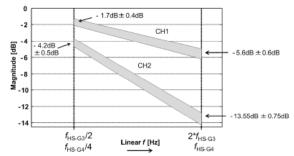

Test 1.1.7 – HS-TX G3 and G4 Differential AC Eye (TEYE-HS-G3/G4-TX, VDIF-AC-HS-G3/G4-TX)

## Agenda

- New specification and CTS changes in 2017

- Eye diagram tests changes and challenges

- MIPI C-PHY<sup>SM</sup>

- MIPI D-PHY<sup>SM</sup>

- MIPI M-PHY<sup>®</sup>

- SSC test

- MIPI D-PHY<sup>SM</sup>

### **Eye Diagram Test - General**

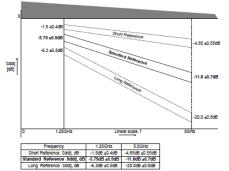

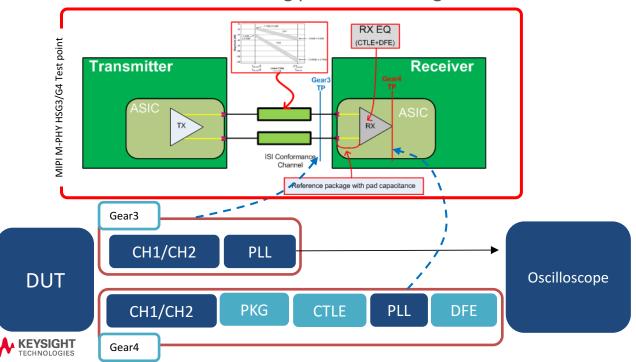

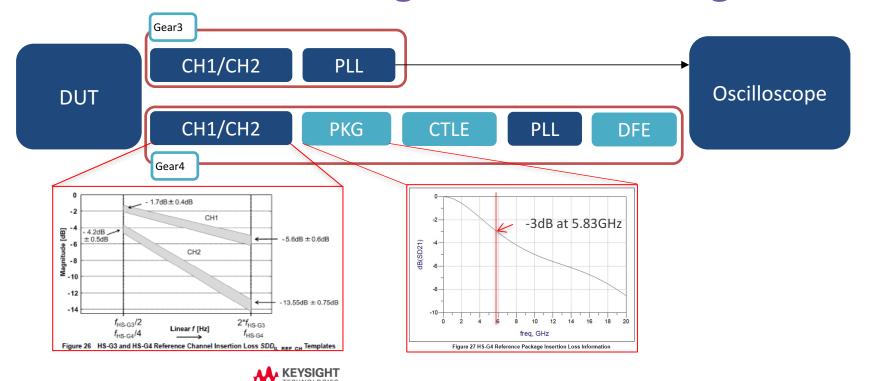

Figure 26 HS-G3 and HS-G4 Reference Channel Insertion Loss SDD<sub>IL REF CH</sub> Templates

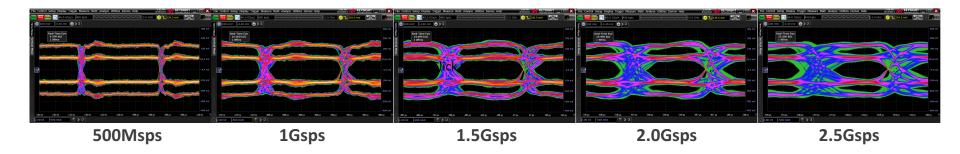

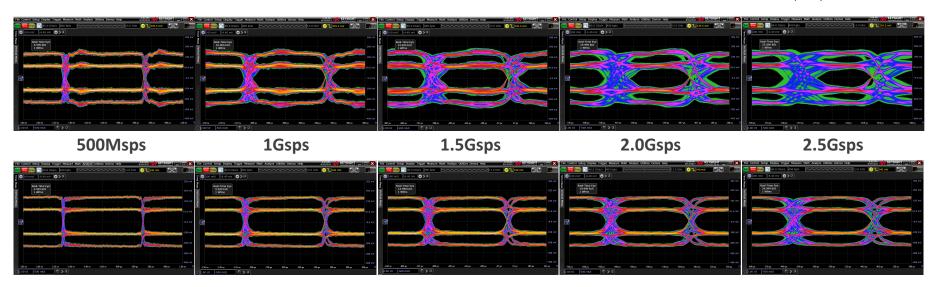

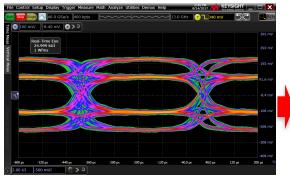

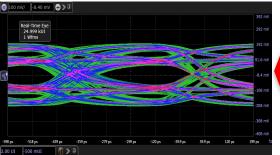

#### **Eye Diagram Test Challenges for MIPI C-PHY/D-PHY**

RTB(Reference Termination Board) can't support new specifications

sps: Symbol Per Second

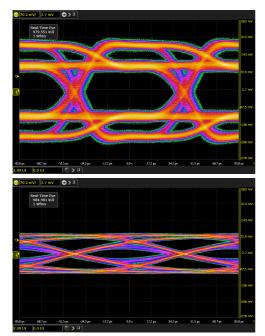

Same data, +/-250mV HS swing, 82ps R/F time, without reference channel However, eye diagram is distorted

MIPI C-PHY RTB

MIPI D-PHY RTB

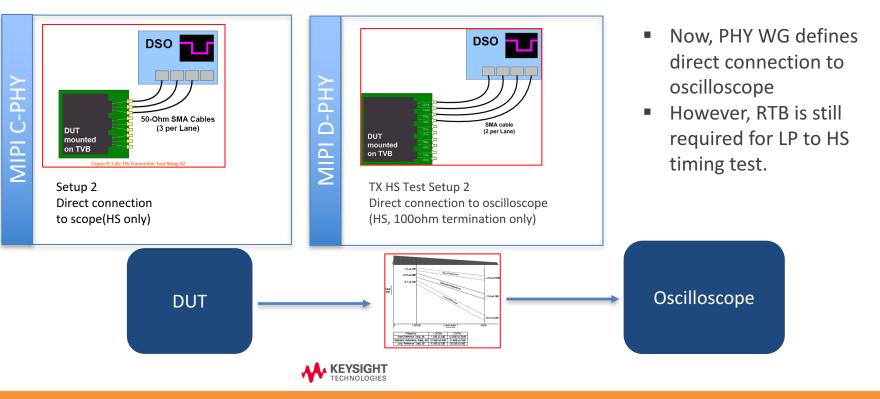

#### MIPI C-PHY/D-PHY Eye Diagram Test

#### **Resolving Issue with Direct Connection**

Direct connection provide more accurate result on tests

sps: Symbol Per Second

Same data, +/-250mV HS swing, 82ps R/F time, without reference channel

## **Chip Design Tip for Testing**

- New MIPI C-PHY v1.1 and D-PHY v2.0 or above require to send both Burst mode and Continuous mode signal on testing, so it is good to consider to implement both mode for easy testing.

- If not, it is not easy to get right test result.

#### MIPI C-PHY CTS Annex B

Notes on the above Test Setup #2: The DUT is connected to the DSO using three high-bandwidth, low loss 50-ohm coaxial cables. 4286 For tests where a reference channel is required, it can either be a physical channel or be 4288 implemented in software on the oscilloscope. Each cable measures the single-ended V<sub>A</sub>, V<sub>B</sub>, or V<sub>C</sub> signal with respect to PCB ground. The DSO serves as the termination, and is designed to have a resistive termination (Z<sub>ID</sub>/2) value of 50 ohms per line, for all lines. The DSO input coupling and/or termination voltage must be set 4291 4292 appropriately for this configuration. . The DUT should be configured to transmit a continuous stream of HS data, because this test setup is suitable for measurements only in the HS mode of operation. 4294 The DSO vertical gain should be optimized so that the DUT signaling spans as much of the 4296 vertical height of the screen as possible.

#### MIPI D-PHY CTS Annex B

Note on the above test setup #2:

- The DUT is connected to the DSO using high-bandwidth, low loss 50Ω SMA cables

- For tests where a reference channel is required, it can either be a physical channel or be implemented in software on the oscilloscope.

- Each cable connected to single-ended + or signal with respect to PCB ground.

- The DSO serves as the termination, and is designed to have a resistive termination(ZID/2) value of 50Ω per line, for all lines. The DSO input coupling and/or termination voltage must be set appropriately to emulate 100Ω termination in real D-PHY.

- The DUT should be configured to transmit a continuous stream of HS data only, because this test setup is suitable for measurements in HS mode of operation with only 100Ω termination emulation.

- The DSO vertical gain should be optimized so that the DUT signaling spans as much of the vertical height

of the screen as possible.

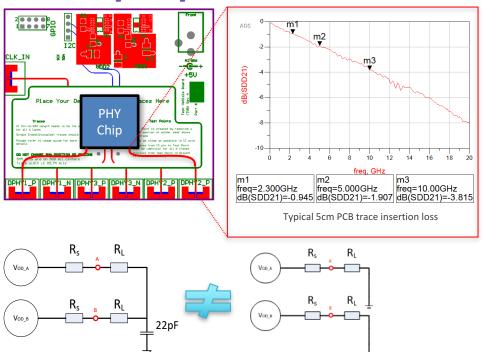

#### **Test Setup Tip 1**

- Prepare Test Fixture (TVB)

with short routing to

connector to reducing

fixture line loss (5cm or less)

or extract S-parameter of

fixture trace when design

TVB

- To emulate 100ohm termination in MIPI PHY, please use external voltage sourced scope or probe to compensate common mode voltage drop and double current consumption

#### **Test Setup Tip 2**

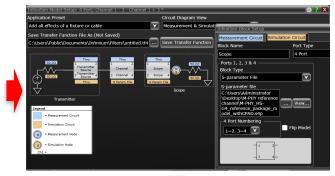

- Use hardware or software channel for eye diagram test, all oscilloscope vendor provide easy tool for software channel embedding, using Sparameter file.

- For MIPI C-PHY and D-PHY, it requires more than 2 lines of channel so software embedding provide more price merit than real hardware channel, also convenient to test

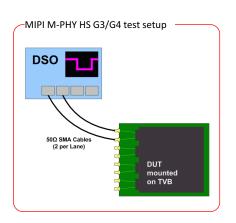

#### MIPI M-PHY Eye Diagram Test

Test setup is same on both HSG3 and HSG4 but testing points has changed.

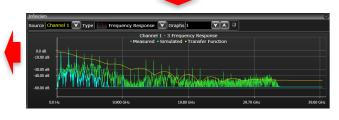

#### MIPI M-PHY Embedding Channel + Package Model

#### Test Setup Tip 3 – and Must for HS Gear4

Reference package plus pad capacitance model is not real material for using, so it is hard to emulate with real PCB or another circuit, so MIPI WG recommends using software embedding function for embedding reference package plus pad capacitance model

## MIPI M-PHY RX Equalizer-CTLE

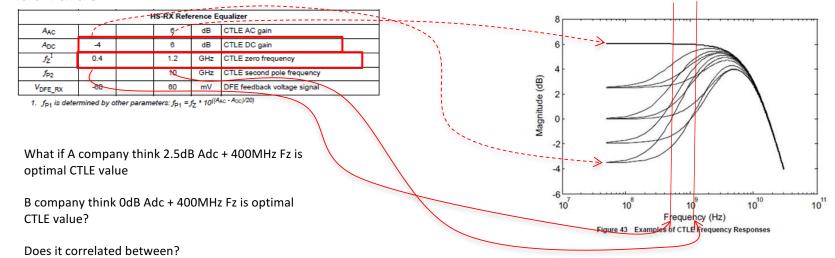

Not likely another application, M-PHY CTLE has vary wide range of zero pole value and Adc value

#### MIPI M-PHY RX Equalizer-CTLE

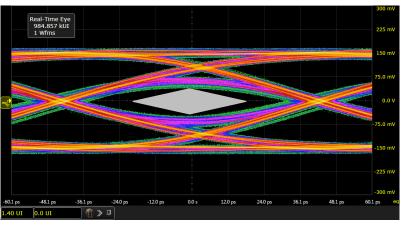

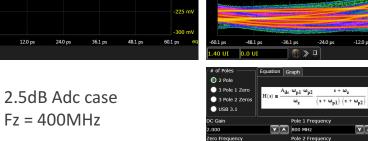

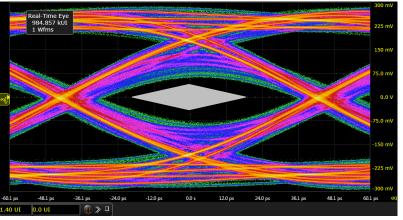

Same waveform but only change Adc value from 2.5dB to 0dB

Adc : CTLE DC gain Fz : CTLE zero frequency

▼ A 10.000 GHz

OdB Adc case Fz = 400MHz

2 Pole

USB 3.1

3 Pole 1 Zero

3 Pole 2 Zeros

Equation Graph

A<sub>dc</sub>·ω<sub>p1</sub>·ω<sub>p2</sub>

▼ ▲ 600 MHz

▼ ▲ 10.000 GHz

Pole 1 Frequency

Pole 2 Frequency

$(s + \omega_{p1}) \cdot (s + \omega_{p2})$

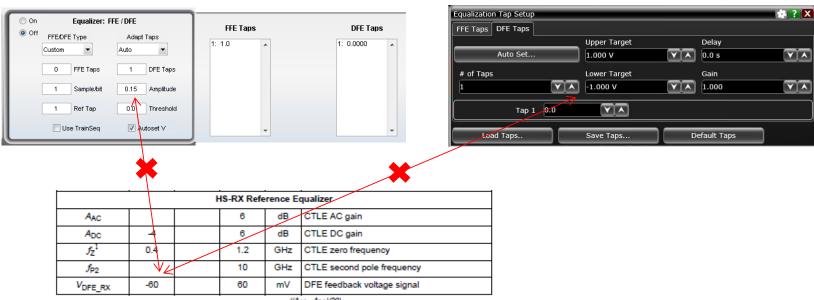

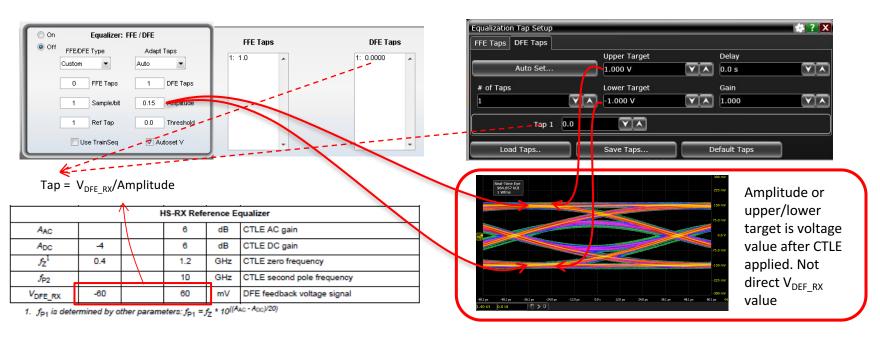

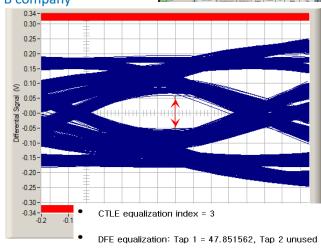

#### MIPI M-PHY RX Equalizer-DFE

Also Oscilloscope's DFE setting is not favor to the customer.

<sup>1.</sup>  $f_{P1}$  is determined by other parameters:  $f_{P1} = f_Z * 10^{((A_{AC} - A_{DC})/20)}$

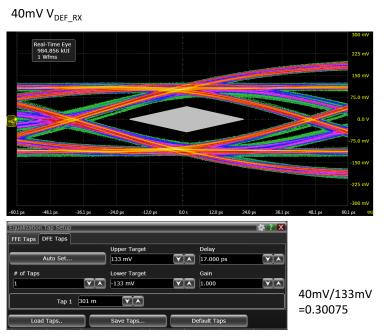

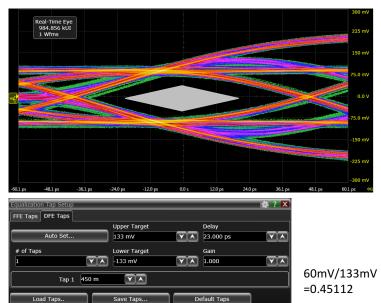

#### MIPI M-PHY RX Equalizer-DFE

Also Oscilloscope's DFE setting is not favor to the customer.

#### MIPI M-PHY RX Equalizer-DFE

V<sub>DEF\_RX</sub>: DFE feedback voltage signal

# **Test Setup Tip 4**

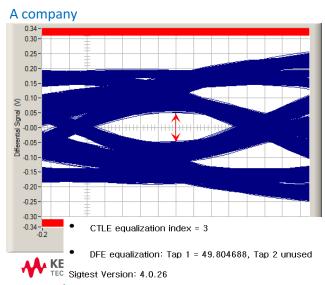

#### Use SigTest tool

Commonly used for High speed digital interface

- USB

- PCle

Provide similar result between oscilloscopes

B company

Sigtest Version: 4.0.26

## Agenda

- New specification and CTS changes in 2017

- Eye diagram tests changes and challenges

- MIPI C-PHY<sup>SM</sup>

- MIPI D-PHY<sup>SM</sup>

- MIPI M-PHY<sup>®</sup>

- SSC test

- MIPI D-PHY<sup>SM</sup>

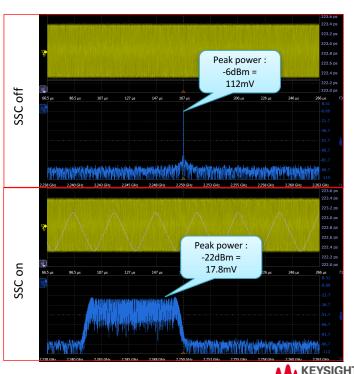

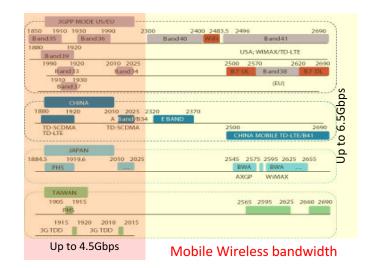

## SSC (Spread Spectrum Clocking) - General

- SSC makes distribution of RF power on signal so that it can reduce interruption to another signals like wireless signal.

- Now MIPI D-PHY fundamental frequency is over 2GHz bandwidth, where lots of wireless signals have used.

- Because of Clock line in MIPI D-PHY, SSC feature is required.

#### SSC (Spread Spectrum Clocking) Test in MIPI D-PHY

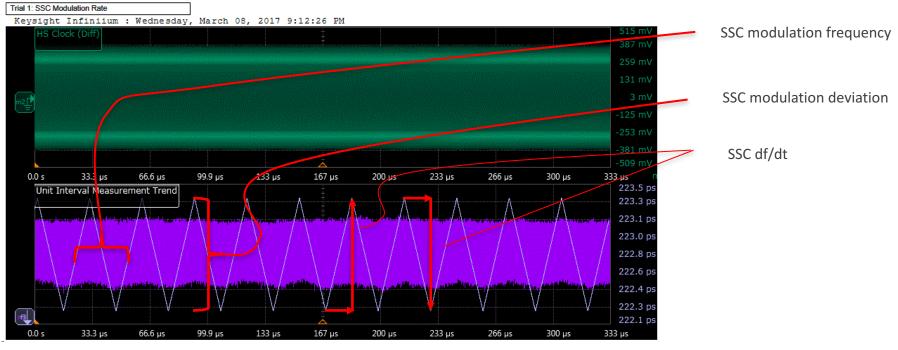

#### SSC in MIPI D-PHY Specification

1276

#### Table 39 Spread Spectrum Clocking Requirements

| Parameter       | Symbol                    | Min   | Max  | Units  | Notes   |          |   |

|-----------------|---------------------------|-------|------|--------|---------|----------|---|

| Modulation Rate | T <sub>SSC_MOD_RATE</sub> | 30    | 33   | kHz    |         |          |   |

| SSC Deviation   | T <sub>SSC_FREQ_DEV</sub> | -5000 | 0    | PPM    | 1, 2    | <b> </b> | • |

| SSC df/dt       | SSC <sub>df/dt</sub>      | N/A   | 1250 | PPM/µs | 3, 4, 5 |          |   |

equirements

#### Note:

- The required SSC deviation is also called "Down-Spread".

- Any implementation with an SSC deviation significantly smaller than 5000 PPM may fail in EMI testing below 1 GHz clock rate (Data Rate < 2 Gbps).</li>

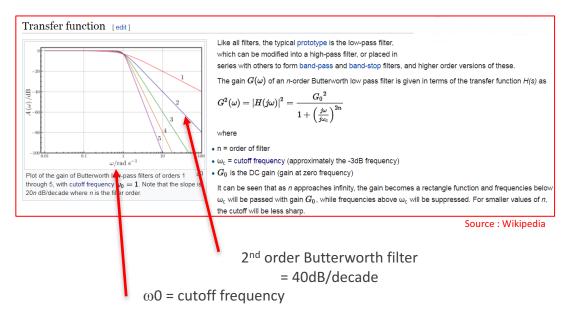

df/dt limit shall be for clock and all data lanes.

- Measured over a 0.5 µs interval using an alternating 010101010... input pattern at highest data rate. The measurements shall be low pass filtered using a filter with 3 dB cutoff frequency that is 60 times the modulation rate. The filter stopband rejection shall be a second order low-pass of 40 dB per decade. Evaluation of the maximum df/dt is achieved by inspection of the low-pass filtered waveform.

- Maximum change rate of 1250 PPM/µs is limiting the absolute value of the df/dt.

### **Chip Design Tip for Testing**

For SSC (spread spectrum clocking), Designer must implement Chip can enable and disable SSC transmission.

#### 10.2.2 Normative Spread Spectrum Clocking (SSC)

All SSC parameters are defined for the HS Clock.

Spread Spectrum Clocking (sometimes referred to as "Spectrum Spread Clocking") is a common technique 1260 where a low frequency modulation is added to the Transmitter's clock to reduce the peak emissions. 1261 All Transmitters conformant to D-PHY v2.0 and above shall support SSC as per Table 39 for data rates 1262 operating above 2.5 Gbps. 1263 All Receivers conformant to D-PHY v2.0 and above shall support SSC as per Table 39 for data rates 1264 operating above 2.5 Gbps. 1265 All Transmitters conformant to D-PHY v2.0 and above shall provide the system integrator with a 1266 mechanism to enable/disable SSC transmissions. 1267 SSC can be used in HS Data Transmission Mode. If used during HS Data Transmission Mode, SSC 1268 transmission shall be consistent during the entire mode. 1269 SSC should not be used in Escape mode. SSC shall be implemented within the Transmitter such that a single modulated profile, single modulation rate and a single SSC deviation is common between the clock and all High-speed data lanes. 1272

KEYSIGHT TECHNOLOGIES

#### **Test Setup Tip 5**

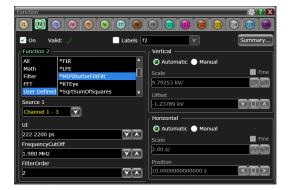

#### Use 2<sup>nd</sup> order Butterworth filter to meet SSC df/dt test condition

Some of Digital oscilloscope are possible to use Matlab code in the oscilloscope itself so that Matlab can apply complicated filter function.

2017

MIPI ALLIANCE

DEVELOPERS

CONFERENCE

BANGALORE, INDIA

MIPI.ORG/DEVCON