# Architecture Overview for Debug

**White Paper**

Version 1.2 13 July 2018

MIPI Board Approved for Public Distribution 29 August 2018

This is an informative document, not a MIPI Specification.

Various rights and obligations that apply solely to MIPI Specifications (as defined in the MIPI Membership Agreement and MIPI Bylaws) including, but not limited to, patent license rights and obligations, do not apply to this document.

The material contained herein is not a license, either expressly or impliedly, to any IPR owned or controlled by any of the authors or developers of this material or MIPI. All materials contained herein are protected by copyright laws, and may not be reproduced, republished, distributed, transmitted, displayed, broadcast or otherwise exploited in any manner without the express prior written permission of MIPI Alliance. MIPI, MIPI Alliance and the dotted rainbow arch and all related trademarks, trade names, and other intellectual property are the exclusive property of MIPI Alliance and cannot be used without its express prior written permission.

This document is subject to further editorial and technical development. USB Type-C<sup>™</sup> is a trademark of the USB Implementers Forum.

#### NOTICE OF DISCLAIMER

The material contained herein is provided on an "AS IS" basis. To the maximum extent permitted by applicable law, this material is provided AS IS AND WITH ALL FAULTS, and the authors and developers of this material and MIPI Alliance Inc. ("MIPI") hereby disclaim all other warranties and conditions, either express, implied or statutory, including, but not limited to, any (if any) implied warranties, duties or conditions of merchantability, of fitness for a particular purpose, of accuracy or completeness of responses, of results, of workmanlike effort, of lack of viruses, and of lack of negligence. ALSO, THERE IS NO WARRANTY OR CONDITION OF TITLE, QUIET ENJOYMENT, QUIET POSSESSION, CORRESPONDENCE TO DESCRIPTION OR NON-INFRINGEMENT WITH REGARD TO THIS MATERIAL.

IN NO EVENT WILL ANY AUTHOR OR DEVELOPER OF THIS MATERIAL OR MIPI BE LIABLE TO ANY OTHER PARTY FOR THE COST OF PROCURING SUBSTITUTE GOODS OR SERVICES, LOST PROFITS, LOSS OF USE, LOSS OF DATA, OR ANY INCIDENTAL, CONSEQUENTIAL, DIRECT, INDIRECT, OR SPECIAL DAMAGES WHETHER UNDER CONTRACT, TORT, WARRANTY, OR OTHERWISE, ARISING IN ANY WAY OUT OF THIS OR ANY OTHER AGREEMENT RELATING TO THIS MATERIAL, WHETHER OR NOT SUCH PARTY HAD ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

The material contained herein is not a license, either expressly or impliedly, to any IPR owned or controlled by any of the authors or developers of this material or MIPI. Any license to use this material is granted separately from this document. This material is protected by copyright laws, and may not be reproduced, republished, distributed, transmitted, displayed, broadcast or otherwise exploited in any manner without the express prior written permission of MIPI Alliance. MIPI, MIPI Alliance and the dotted rainbow arch and all related trademarks, service marks, tradenames, and other intellectual property are the exclusive property of MIPI Alliance Inc. and cannot be used without its express prior written permission. The use or implementation of this material may involve or require the use of intellectual property rights ("IPR") including (but not limited to) patents, patent applications, or copyrights owned by one or more parties, whether or not members of MIPI. MIPI does not make any search or investigation for IPR, nor does MIPI require or request the disclosure of any IPR or claims of IPR as respects the contents of this material or otherwise.

Without limiting the generality of the disclaimers stated above, users of this material are further notified that MIPI: (a) does not evaluate, test or verify the accuracy, soundness or credibility of the contents of this material; (b) does not monitor or enforce compliance with the contents of this material; and (c) does not certify, test, or in any manner investigate products or services or any claims of compliance with MIPI specifications or related material.

Questions pertaining to this material, or the terms or conditions of its provision, should be addressed to:

MIPI Alliance, Inc. c/o IEEE-ISTO

445 Hoes Lane, Piscataway New Jersey 08854, United States

Attn: Managing Director

# **Contents**

| C  | ontents             | 5                                                            | iii  |

|----|---------------------|--------------------------------------------------------------|------|

| Fi | igures              |                                                              | v    |

| T  | ables               |                                                              | vii  |

| R  | elease l            | History                                                      | viii |

| 1  |                     | view                                                         |      |

| 1  | 1.1                 | Scope                                                        |      |

| 2  |                     | •                                                            |      |

| 2  | 2.1                 | ninology                                                     |      |

|    | 2.2                 | Abbreviations                                                |      |

|    | 2.3                 | Acronyms                                                     |      |

| 3  |                     | rences                                                       |      |

| 4  |                     | ıg System                                                    |      |

| 7  | 4.1                 | System Framework                                             |      |

|    | 4.2                 | The MIPI Debug and Test System                               |      |

| 5  | Debi                | ıg Physical Interfaces (DPI)                                 |      |

|    | 5.1                 | Parallel Trace Interface (PTI) Specification                 |      |

|    | 5.1.1               | Trace and Debug Overview                                     |      |

|    | 5.1.2               | Relationship to MIPI Debug Architecture                      | 16   |

|    | 5.1.3               | Trace Scenarios                                              | 17   |

|    | 5.1.4               | Detailed Specification                                       | 21   |

|    | 5.2                 | High-speed Trace Interface (HTI) Specification               | 22   |

|    | 5.2.1               | Overview                                                     |      |

|    | 5.2.2               | Relationship to the MIPI Debug Architecture                  |      |

|    | 5.2.3               | HTI Details                                                  |      |

|    | 5.2.4               | Detailed Specification                                       |      |

|    | 5.3                 | Debug Connector Recommendations                              |      |

|    | 5.3.1               | Dedicated Debug Connector Overview                           |      |

|    | 5.3.2               | Relationship to the MIPI Debug Architecture                  |      |

|    | 5.3.3               | Basic Debug Connectors                                       |      |

|    | 5.3.4               | High-Speed Parallel Trace Connectors  Detailed Documentation |      |

|    | 5.3.5<br><b>5.4</b> | Narrow Interface for Debug and Test (NIDnT) Specification    |      |

|    | 5.4.1               | Overview                                                     |      |

|    | 5.4.2               | Relationship to the MIPI Debug Architecture                  |      |

|    | 5.4.3               | NIDnT Details                                                |      |

|    | 5.4.4               | Debug and Test Capabilities Supported by NIDnT Overlay Modes |      |

|    | 5.4.5               | Functional Interfaces that are NIDnT Candidates              |      |

|    | 5.4.6               | Detailed Specification                                       |      |

| 6  | Dehi                | ig Access and Control Subsystem (DACS)                       |      |

| J  | 6.1                 | IEEE 1149.7 Debug and Test Interface Specification           |      |

|    | 6.1.1               | Relationship to MIPI Debug Architecture                      |      |

|    | 6.1.2               |                                                              |      |

| 6.2        | SneakPeek Specification                            | 34 |

|------------|----------------------------------------------------|----|

| 6.2.1      | Relationship to MIPI Debug Architecture            | 34 |

| 6.2.2      | 2 Overview                                         | 34 |

| 6.2.3      | 3 TinySPP                                          | 37 |

| 6.2.4      | Detailed Specifications                            | 37 |

| 7 Deb      | ug Instrumentation and Visibility Subsystem (DIVS) | 38 |

| <b>7.1</b> | Instrumentation and Visibility Subsystem Overview  |    |

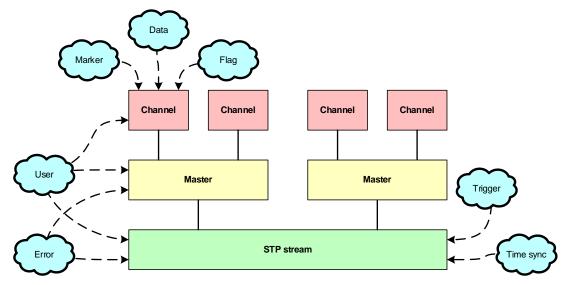

| 7.2        | System Trace Protocol (STP) Specification          | 38 |

| 7.2.1      | Relationship to MIPI Debug Architecture            | 39 |

| 7.2.2      | Protocol Overview                                  | 39 |

| 7.2.3      | B Detailed Specification                           | 41 |

| 7.3        | Trace Wrapper Protocol (TWP) Specification         | 42 |

| 7.3.1      | Overview                                           | 42 |

| 7.3.2      | Relationship to MIPI Debug Architecture            | 43 |

| 7.3.3      | 3 TWP Features                                     | 43 |

| 7.3.4      | TWP Description                                    | 44 |

| 7.3.5      | 5 Layers                                           | 44 |

| 7.3.6      | 5 Detailed Specification                           | 44 |

| 7.4        | Gigabit Trace (GbT)                                | 45 |

| 7.4.1      | Summary                                            | 45 |

| 7.4.2      | Relationship to MIPI Debug Architecture            | 45 |

| 7.4.3      | Gigabit Trace System Overview                      | 46 |

| 7.4.4      | Requirements Summary                               | 47 |

| 7.4.5      | Detailed Specification                             | 47 |

| 7.5        | STP and TWP in the DIVS                            | 48 |

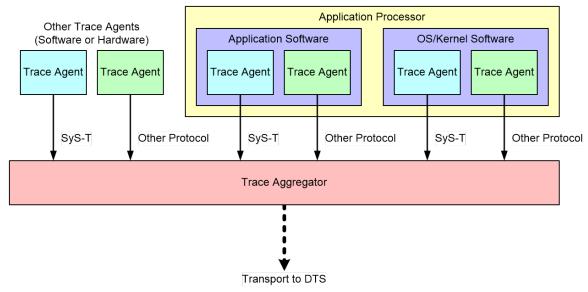

| <b>7.6</b> | System Software Trace (SyS-T) Specification        | 50 |

| 7.6.1      | Overview                                           | 50 |

| 7.6.2      | Relationship to MIPI Debug Architecture            | 50 |

| 7.6.3      | B Usage                                            | 51 |

| 7.6.4      | SyS-T Instrumentation Library                      | 51 |

| 7.6.5      | Detailed Specification                             | 52 |

| 8 Deb      | ug Network Interfaces (DNI)                        | 53 |

| 8.1        | Gigabit Debug (GbD) Specification                  |    |

| 8.1.1      | Overview                                           | 53 |

| 8.1.2      | Relationship to MIPI Debug Architecture            | 55 |

| 8.1.3      | •                                                  |    |

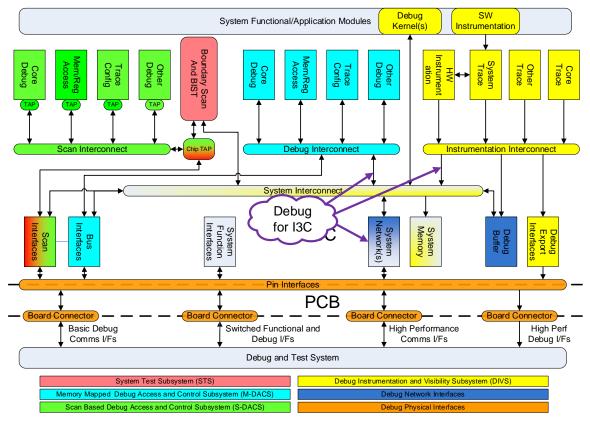

| 8.2        | Debug for I3C (ongoing)                            |    |

| 8.2.1      |                                                    |    |

| 8.2.2      |                                                    |    |

| 8.2.3      | •                                                  |    |

# **Figures**

| Figure 1 MIPI Debug Generic System Framework                                     | 12 |

|----------------------------------------------------------------------------------|----|

| Figure 2 MIPI Debug Documentation and the Debug Architecture                     | 13 |

| Figure 3 Example MIPI System Overview                                            | 14 |

| Figure 4 PTI in the MIPI Debug Architecture                                      | 16 |

| Figure 5 Example System with PTI                                                 | 17 |

| Figure 6 PTI Layers within a System                                              | 18 |

| Figure 7 Multi-Point PTI with 4-Pin Trace and Four Devices Sharing the Connector | 20 |

| Figure 8 Multi-Point PTI with 4-Pin Trace and Two Devices Sharing the Connector  | 21 |

| Figure 9 HTI in the MIPI Debug Architecture                                      | 22 |

| Figure 10 Connectors in the MIPI Debug Architecture                              | 24 |

| Figure 11 Basic Debug PCB (left) and Cable End Connector (34-pin Samtec FTSH)    | 25 |

| Figure 12 Recommended Samtec QSH/QTH Connector                                   | 25 |

| Figure 13 NIDnT in the MIPI Debug Architecture                                   | 27 |

| Figure 14 Example of System with a Dedicated Debug Interface                     | 28 |

| Figure 15 Example of System with NIDnT Capability                                | 29 |

| Figure 16 DTS to TS Connectivity                                                 | 32 |

| Figure 17 IEEE 1149.7 in the MIPI Debug Architecture                             | 33 |

| Figure 18 SneakPeek in the MIPI Debug Architecture                               | 34 |

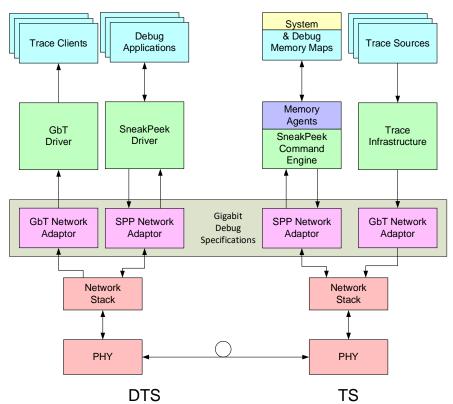

| Figure 19 Overview of SneakPeek System                                           | 35 |

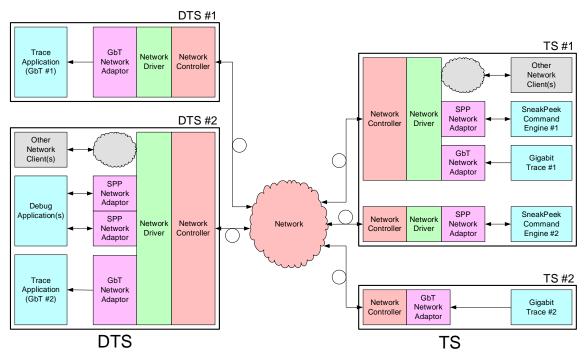

| Figure 20 SneakPeek Protocol and Network Stacks in DTS and TS                    | 36 |

| Figure 21 STP in the MIPI Debug Architecture                                     | 39 |

| Figure 22 Conceptual Hierarchy of STP Masters and Channels                       | 40 |

| Figure 23 STM in a Target System                                                 | 40 |

| Figure 24 Example STP Packet Sequence                                            | 41 |

| Figure 25 TWP in the MIPI Debug Architecture                                     | 43 |

| Figure 26 Example Use Cases for Layers T1, T2 and T3                             | 44 |

| Figure 27 Gigabit Trace and the MIPI Debug Architecture                          | 45 |

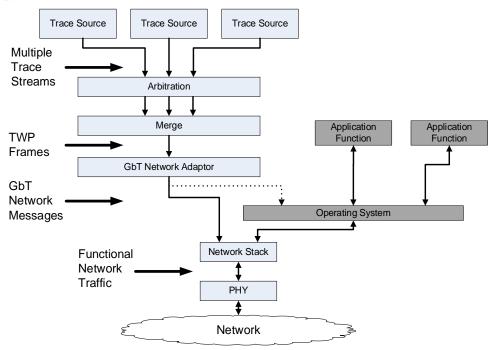

| Figure 28 Typical GbT Configuration and Data Flow (TS)                           | 46 |

| Figure 29 Typical GbT Configuration and Data Flow (DTC and DTS)                  | 47 |

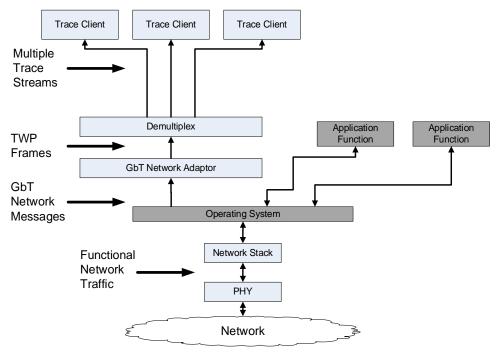

| Figure 30 Example Trace Architecture                                             | 49 |

| Figure 31 SyS-T in the MIPI Debug Architecture                                   | 50 |

| Architecture       | Overview   | for | Debug |

|--------------------|------------|-----|-------|

| 1 II CIII CC LUI C | O VCI VICW | 101 | DCUUE |

| Figure 32 SyS-T Instances in a Target System           | 51 |

|--------------------------------------------------------|----|

| Figure 33 Gigabit Debug Functional Block Diagram       | 53 |

| Figure 34 GbD in a Multiple-Node Network               | 54 |

| Figure 35 Gigabit Debug and the MIPI Architecture      | 55 |

| Figure 36 Debug for I3C in the MIPI Debug Architecture | 57 |

| Version 1.2 | Architecture Overview for Debug |

|-------------|---------------------------------|

| 13-Jul-2018 |                                 |

# **Tables**

Table 1 Summary of Test/Debug Capabilities Supported by NIDnT ......30

# **Release History**

| Date       | Version | Description            |

|------------|---------|------------------------|

| 2014-02-14 | v1.0    | Board approved release |

| 2016-09-29 | v1.1    | Board approved release |

| 2018-08-29 | v1.2    | Board approved release |

#### 1 Overview

#### 1.1 Scope

1

3

5

8

9

10 11

12

13

14

15

16

17

18

19

20

2.1

22

23

24

25

2627

2.8

Recent technological developments have resulted in a quantum leap in the complexity of SoCs. Systems that were formerly deployed on one or more PCBs are now being instantiated as single discrete devices. While this trend is in general a boon to manufacturers and consumers of mobile systems, it has greatly increased the complexity of system debug and optimization. Signals and interfaces that used to be visible at test points on a PCB are now deeply embedded inside a SoC. The use of tried and true methods of probing buses and signals with dedicated Debug and Test equipment is now virtually impossible.

This increase in debug complexity is being addressed by IP vendors, SoC developers, OEMs and tools vendors. New technologies are being deployed that provide the visibility required in these complex and deeply embedded designs. In order to maximize the utility and efficiency of debug, converging on common interfaces and protocols used by these new technologies is essential. There are efforts to standardize debug effort across certain industry spaces, but there was not such an effort addressing the particular debug needs of the mobile space.

To meet this need, the MIPI Debug Working Group (Debug WG) are developing a portfolio of standards and other documents that address the particular needs of debug in the mobile and mobile-influenced space. Some of the areas of focus are listed below.

- Minimizing the pin cost and increasing the performance of the basic debug interface

- Increasing the bandwidth, capability and reliability of the high performance interfaces used to export high bandwidth, unidirectional debug data (e.g. processor trace data) to the debug tools

- Deploying debug connectors that are physically robust and have the performance required for the high bandwidth demands of modern debug technologies

- Developing generic trace protocols that allow many different on chip trace sources to share a single trace data flow to the debug tools

- Maximizing debug visibility in fielded systems by reusing some of the functional interfaces/connectors for debug

- Utilizing the new high bandwidth functional interfaces being deployed on mobile systems as a transport for debug

This document provides an overview of the efforts to address these goals and provides summaries of the documents that address them in detail.

## 2 Terminology

#### 2.1 Definitions

- 29 **1149.1:** Short for IEEE 1149.1. See *[IEEE01]*.

- 30 **1149.7:** Short for IEEE 1149.7. See [IEEE02].

- Application Function: All functions of the TS other than Debug and Test Functions.

- Application Processor: A programmable CPU (or CPU-based system on a chip (SoC) which may include

- other programmable processors such as DSPs), primarily, but not necessarily exclusively, programmed to

- coordinate the application processing and user interface processing in a mobile terminal.

- Application Software: Used here to mean the target resident code that runs on the target processor. This includes the operating system as well as the program(s) running with the OS.

- Basic Debug Communication: Debug communication needed through an 1149.1 (or equivalent) port only

- to manage basic debug communication functions such as run control, hardware breakpoints and

- watchpoints, and examining system state.

- **Boundary Scan:** A production test mechanism where interconnects between chips or logic blocks in an

- SoC are verified by forcing known test patterns into the system via a serial scan interface, activating a test

- mode, and then scanning out the resultant values to test against expected results.

- Built-in Self-Test (BIST): On-chip logic function that verifies all or a portion of the internal functionality

- of a SoC during production tests. BIST logic requires minimal interaction with external test infrastructures

- and speeds up verification of complex SoCs.

- Debug: To detect, trace, and eliminate SW mistakes. Also used to get an insight into an embedded

- 47 processor system for performance measurements and debug of system level hardware. Used in this

- document in an inclusive way that encompasses stop/start/break/step debugging as well as non-halting

- methods such as trace.

- Debug Access and Control Subsystem (DACS): The subsystem that provides a path for the DTS to obtain

- direct access to application visible system resources (registers and memory).

- Debug and Test Controller (DTC): The hardware system that is responsible for managing

- communications with a system being debugged (the Target System).

- Debug and Test Function: A block of on-chip logic that carries out a debug function such as run control,

- providing debug access to system resources, Processor Trace, or test capability.

- Debug and Test Interface (DTI): The interface between the Debug and Test System (DTS) and the Target

- 57 System (TS). The interface enables access to basic debug communication, the trace port, streaming data

- (input and output), and other debug or test capabilities.

- **Debug and Test System (DTS):** The combined HW and SW system that provides a system developer

- debug visibility and control when connected to a Target System. The system incorporates:

- A host PC, workstation or other processing system, running the debug or test software, controlling

- the Debug and Test Controller. See also: Debug and Test Controller (DTC).

- Debugger: The debugger software, part of the Debug and Test System. It interacts with the Debug

- and Test Controller and provides the (graphical) user interface for operating the Debug and Test

- Controller (like commanding single step, setting breakpoints, memory display/modify, trace

- reconstruction, etc.)

- Debug and Test Target (DTT): A component in the Target System that implements one or more Debug

- and Test Functions. The interfaces to Debug and Test Targets, where different from the DTI, are not within

- the scope of this specification. Examples include the debug control module on a CPU, debug interface to

- system memory, or the configuration interface to an on-chip trace module.

59

61

62

63

13-Jul-2018

- 71 **Debug Instrumentation and Visibility Subsystem (DIVS):** The subsystem that provides communication

- and storage of data generated by debug instrumentation modules (like processor and system trace) in the

- 73 target system.

79

- Debug Physical Interfaces (DPI): The chip and board level interfaces used to connect the DTC to the onchip debug functions.

- Double Data Rate (DDR): A parallel data interface that provides valid data on both the rising and falling edge of the interface clock.

- 78 **Electrical:** The definition of:

- Signal voltage levels, current drain and drive strength on inputs, outputs, and bi-directional pins

- Rise and fall times and expected loads for device pins.

- Function Assignment: The mapping of functions to signals (and thus to pins as per the current Pin Assignment, e.g. Debug port pin [5] = CLK = TRACECLK.)

- Function Select: The method by which the Basic Debug Communication channel can be switched between use for Debug Functions and use for operations needed to configure the debug system.

- Gigabit Trace (GbT): A system architecture that supports transporting trace data over high-speed networks and transports. See [MIPI04a].

- Gigabit Debug (GbD): A set of network-specific adaptor specifications for mapping SneakPeek and Gigabit Trace to various functional networks.

- Hardware Protocol: The signal protocol required for a Debug and Test Controller to correctly move control or data information between the DTC and Target System.

- High Bandwidth Connection: A Mating Connection, Pin Assignment and Electrical specification for full

- functionality, high frequency, higher pin count connection between the Target System and the Debug and

- 93 Test Controller / TPA.

- High-speed Trace Interface (HTI): The transport specification that defines the electrical and timing characteristics of high-speed serial trace export interfaces. See [MIP109].

- 96 **IEEE 1149.7 (basic debug communication):** Enhanced IEEE1149.1 Debug and Test communication

- 97 standard, configurable from 4 to 2 pins. The IEEE 1149.7 interface can be viewed as providing

- functionality enhanced compared to 1149.1 for Basic Debug Communication and test and with fewer pins.

- A two-way communication channel for exclusive Debug and Test uses. See [IEEE02].

- Intellectual Property (IP): any patents, patent rights, trademarks, service marks, registered designs,

- topography or semiconductor mask work rights, applications for any of the foregoing, copyrights,

- unregistered design rights, trade secrets and know-how and any other similar protected rights in any

- country. Any IP definition by MIPI By-Laws will supersede this local one.

- Low Pin Count Connection: A Mating Connection, Pin Assignment and Electrical specification for Basic

- Debug Communication and limited Trace Port functionality, lower frequency, low pin count connection

- between the Target System and the Debug and Test Controller / TPA.

- Mating Connection: The connector to be used, defined by specific manufacturer and part number. The

- required keep out area for board design to enable unobstructed connector mating. The definition of cable

- characteristics and terminations may include the characteristics of a connection from the point it leaves an

- output buffer in a chip on the target or host side, routing on a printed circuit board on the DTC or Target

- System side, cabling between the signal source and destination, and any connections (via connectors) in the

- signal path.

- Min-Pin: An interface for Basic Debug Communication with a minimal number of pins (2), using either

- 114 IEEE 1149.7, SWD or I3C.

- Mode Select: A method for selecting a different Mating Connection, a different operating mode, a different

- electrical mode or a combination of these, for example switching between 1149.1 and 1149.7.

- Narrow Interface for Debug and Test (NIDnT): A signal-mapping specification that defines how to reuse the functional interfaces commonly available on fielded mobile systems for debug. See [MIP105].

- Nexus: An IEEE-ISTO 5001<sup>TM</sup> standard interface for embedded processor debug. The Nexus standard includes support for Basic Debug Communication as well as instruction and data tracing. See *[ISTO01]*.

- Other Debug: Debug functions not covered by 1149.1, 1149.7 or the Trace Port for example off-chip memory emulation.

- Parallel Trace Interface (PTI): The interface specification that defines the electrical and timing characteristics of trace export interfaces that consist of a single clock and multiple data signals. See [MIPI02].

- Pin Assignment: The mapping of signals to pins, e.g., SIGNAL\_NAME on pin number N. This may include restrictions on allowable pin assignments.

- Processor Trace: The non-intrusive capture and logging of the activity of an embedded processor and the subsystem in which the processor resides. Processor trace generally consists of one or more of the following trace types, but it is not limited to these:

- Instruction (PC) Trace Application execution flow can be reconstructed by processing the logged information

- Data Trace Data access activity is captured at the processor boundary

- The captured data is encoded for efficiency and this data is stored on-chip for later upload or immediately transmitted through a chip interface to an off-chip receiver.

- Return Test Clock (RTCK): A non-standard extension to 1149.1 that provides a feedback path for pacing transaction on the interface.

- Serial Wire Debug (SWD): An interface used for Basic Debug Communication. See [ARM01].

- Series Scan Topology: A connection scheme where the control signals on the debug interfaces are connected in parallel, but the data signals are daisy chained.

- Silicon Test Subsystem (STS): This subsystem supports communication between the DTS and the on-chip logic used for production test (boundary scan, BIST, etc.).

- Star Scan Topology: A connection scheme where both the control and data signals on the debug interfaces are connected in parallel.

- System Software Trace (SyS-T): A format for transporting software traces and debugging information

- between a mobile or mobile influenced target system (TS) running embedded software, and a debug and

- test system (DTS), typically a computer running one or more debug and test applications (debuggers and trace tools).

- System Trace Module (STM): A system trace interface with capabilities to export SW (printf type) and

- HW generated traces (e.g., PC trace and memory dumps). Typical implementation is 4-bit parallel double

- data rate. The STM uses a nibble-oriented protocol called STP. See [MIPI03].

- System Trace Protocol (STP): The protocol used with STM. See [MIPI03].

- System on a Chip (SoC): An electronic system in which all (or most of) the functional modules are integrated on a single silicon die and packaged as a single chip.

- System Trace: In the context of this document, system trace refers to SW Instrumentation Trace and HW Instrumentation Trace.

- SW Instrumentation Trace Message output from instrumented application code.

- HW Instrumentation Trace Messages triggered by transactions/events on the SoC infrastructure(s) and other HW modules in the system.

- Target System (TS): The system being debugged, up to the Debug and Test Interface (DTI). The TS might be a discrete device (a chip) or a collection of 1 to N discrete devices grouped on a board or collection of boards. The TS might also contain 0 to N individual Debug and Test Targets.

- Test Access Port (TAP): The on-chip interface to Debug and Test resources. Both 1149.1 and 1149.7

- support the concept of a Test Access Port.

- Timing: The AC characteristics of debug signals at the pins of the target device. Includes skew, jitter, rise

- and fall times, data/clock alignment, set-up and hold times. While this is shown to be common between all

- connectors, there will likely be some variation, for example the Gigabit connector might not have separate

- clock and data pins.

- **Trace:** A form of debugging where processor or system activity is made externally visible in real-time or

- stored and later retrieved for viewing by an applications developer, applications program, or, external

- equipment specializing observing system activity.

- 172 **Trace Channel:** A group of one or more signals and a clock that move trace information from the TS to the

- DTS. There may be more than one Trace Channel between the TS and DTS.

- 174 **Trace Data Protocol:** The implementation-specific encoding of a particular type of trace by a particular

- 175 module.

- Trace Port: An output port for the transmission of real-time data indicating the operation of the target (e.g.,

- program execution and/or data bus transactions). Data transmitted across the Trace Port may be generated

- by hardware, software instrumentation, or by a mixture of the two. This does not include trace collected on-

- chip for later upload.

- Trace Port Analyzer (TPA): An external hardware unit for collecting data transmitted from the Trace Port.

- The data might be stored locally in real time before uploading to the host debug tools for later analysis by

- the user, e.g., a logic analyzer or a unit customized to record trace information would both qualify.

- Trace Wrapper Protocol (TWP): A protocol that wraps trace from different sources in to a single stream

- for simultaneous capture by a single TPA. See [MIPI04] and [MIPI04a].

- 185 **Trigger:** An indication that a specific system event has occurred. A trigger may be an input to the TS, a

- signal within the TS, or an output from the TS. The response to the trigger is determined by the entity to

- which the trigger is sent.

#### 2.2 Abbreviations

- 188 e.g. For example (Latin: exempli gratia)

- i.e. That is (Latin: id est)

#### 2.3 Acronyms

| 190 | AC   | Alternating Current                            |

|-----|------|------------------------------------------------|

| 191 | BIST | Built-in Self-Test                             |

| 192 | CCC  | Common Command Code                            |

| 193 | CPU  | Central Processing Unit                        |

| 194 | DACS | Debug Access and Control Subsystem             |

| 195 | DDR  | Double Data Rate                               |

| 196 | DFT  | Design for Test                                |

| 197 | DIP  | Data Integrity Package                         |

| 198 | DIVS | Debug Instrumentation and Visibility Subsystem |

| 199 | DNI  | Debug Network Interfaces                       |

| 200 | DPI  | Debug Physical Interfaces                      |

| 201 | DSP     | Digital Signal Processor                          |

|-----|---------|---------------------------------------------------|

| 202 | DTC     | Debug and Test Controller                         |

| 203 | DTI     | Debug and Test Interface                          |

| 204 | DTS     | Debug and Test System                             |

| 205 | DTT     | Debug and Test Target                             |

| 206 | GbD     | Gigabit Debug                                     |

| 207 | GbT     | Gigabit Trace                                     |

| 208 | HTI     | High-speed Trace Interface                        |

| 209 | HW      | Hardware                                          |

| 210 | I3C     | Improved Inter Integrated Circuit                 |

| 211 | ID      | Identifier                                        |

| 212 | IEEE    | Institute of Electrical and Electronics Engineers |

| 213 | IP      | Intellectual Property                             |

| 214 | IPS     | Internet Protocol Sockets                         |

| 215 | IPR     | Intellectual Property Rights                      |

| 216 | ISTO    | Industry Standards and Technology Organization    |

| 217 | JTAG    | Joint Test Action Group                           |

| 218 | microSD | Micro Secure Digital                              |

| 219 | MMC     | MultiMediaCard                                    |

| 220 | NIDnT   | Narrow Interface for Debug and Test               |

| 221 | nTRST   | Not Test Reset                                    |

| 222 | OFM     | Original Functional Mode                          |

| 223 | OS      | Operating System                                  |

| 224 | PC      | Personal Computer or Program Counter              |

| 225 | PCB     | Printed Circuit Board                             |

| 226 | PHY     | Physical Interface                                |

| 227 | POR     | Power on Reset                                    |

| 228 | PTI     | Parallel Trace Interface                          |

| 229 | RF      | Radio Frequency                                   |

| 230 | RTCK    | Return Test Clock                                 |

| 231 | SIM     | Subscriber Identity Module                        |

| 232 | SoC     | System on a Chip                                  |

| 233 | SPP     | SneakPeek Protocol                                |

| 234 | SPTB    | SneakPeek Transfer Block                          |

| 235 | STM     | System Trace Module                               |

|     |         |                                                   |

# Version 1.2 13-Jul-2018

| 236 | STP   | System Trace Protocol         |

|-----|-------|-------------------------------|

| 237 | STS   | Silicon Test Subsystem        |

| 238 | SW    | Software                      |

| 239 | SWD   | Serial Wire Debug             |

| 240 | SyS-T | System Software Trace         |

| 241 | TAP   | Test Access Port              |

| 242 | TCK   | Test Clock                    |

| 243 | TCKC  | Test Clock Compact            |

| 244 | TCP   | Transmission Control Protocol |

| 245 | TDI   | Test Data Input               |

| 246 | TDIC  | Test Data Input Compact       |

| 247 | TDO   | Test Data Output              |

| 248 | TDOC  | Test Data Output Compact      |

| 249 | TDP   | Trace Data Protocol           |

| 250 | TMS   | Test Mode Select              |

| 251 | TMSC  | Test Mode Select Compact      |

| 252 | TPA   | Trace Protocol Analyzer       |

| 253 | TS    | Target System                 |

| 254 | TWP   | Trace Wrapper Protocol        |

| 255 | UDP   | User Datagram Protocol        |

| 256 | USB   | Universal Serial Bus          |

| 257 | WG    | Working Group                 |

|     |       |                               |

# 3 References

| 258<br>259        | [MIPI01]  | MIPI Alliance Recommendation for Debug and Trace Connectors, version 1.10.00 and higher, MIPI Alliance, Inc., 16 March 2011.                                                                                                                                                                              |

|-------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 260<br>261        | [MIPI02]  | MIPI Alliance Specification for Parallel Trace Interface (PTI <sup>SM</sup> ), version 2.0, MIPI Alliance, Inc., 3 May 2011.                                                                                                                                                                              |

| 262<br>263        | [MIPI03]  | MIPI Alliance Specification for System Trace Protocol (STP <sup>SM</sup> ), version 2.2, MIPI Alliance, Inc., 21 August 2015.                                                                                                                                                                             |

| 264<br>265        | [MIPI04]  | MIPI Alliance Specification for Trace Wrapper Protocol (TWP <sup>SM</sup> ), version 1.00.00, MIPI Alliance, Inc., 23 February 2010.                                                                                                                                                                      |

| 266<br>267        | [MIPI04a] | MIPI Alliance Specification for Trace Wrapper Protocol (TWP <sup>SM</sup> ), version 1.1, MIPI Alliance, Inc., 3 September 2014.                                                                                                                                                                          |

| 268<br>269        | [MIPI05]  | MIPI Alliance Specification for Narrow Interface for Debug and Test (NIDnT <sup>SM</sup> ), version 1.2, MIPI Alliance, Inc., 17 August 2017.                                                                                                                                                             |

| 270<br>271        | [MIPI06]  | MIPI Alliance Specification for SneakPeek <sup>SM</sup> Protocol (SPP <sup>SM</sup> ), version 1.0 and higher, MIPI Alliance, Inc., 3 March 2015.                                                                                                                                                         |

| 272<br>273        | [MIPI07]  | MIPI Alliance Specification for Gigabit Debug for USB, version 1.1, MIPI Alliance, Inc., 12 October 2017.                                                                                                                                                                                                 |

| 274<br>275        | [MIPI08]  | MIPI Alliance Specification for Gigabit Debug for Internet Protocol Sockets, version 1.0, MIPI Alliance, Inc., 20 May 2016.                                                                                                                                                                               |

| 276<br>277        | [MIPI09]  | MIPI Alliance Specification for High-Speed Trace Interface (HTI <sup>SM</sup> ), version 1.0, MIPI Alliance, Inc., 10 March 2016.                                                                                                                                                                         |

| 278<br>279        | [MIPI10]  | MIPI Alliance Specification for System Software Trace (SyS-T <sup>SM</sup> ), version 1.0, MIPI Alliance, Inc., 1 December 2017.                                                                                                                                                                          |

| 280<br>281        | [MIPI11]  | MIPI System Software Trace (MIPI SyS-T) – Example Code, <a href="https://github.com/MIPI-Alliance/public-mipi-sys-t">https://github.com/MIPI-Alliance/public-mipi-sys-t</a> , MIPI Alliance, Inc., last accessed 4 April 2018.                                                                            |

| 282               | [MIPI12]  | MIPI Alliance Specification for Debug for 13C, version 1.0, MIPI Alliance, Inc., In Press.                                                                                                                                                                                                                |

| 283               | [MIPI13]  | MIPI Alliance Specification 13CSM, version 1.1, MIPI Alliance, Inc., In Press.                                                                                                                                                                                                                            |

| 284               | [MIPI14]  | MIPI Alliance Specification I3C Basic SM, version 1.0, MIPI Alliance, Inc., In Press.                                                                                                                                                                                                                     |

| 285<br>286        | [IEEE01]  | IEEE Std 1149.1 <sup>TM</sup> -2001, <i>Standard for Test Access Port and Boundary-Scan Architecture</i> , Institute of Electrical and Electronic Engineers, 2001.                                                                                                                                        |

| 287<br>288<br>289 | [IEEE02]  | IEEE Std 1149.7 <sup>TM</sup> -2009, <i>Standard for Reduced-Pin and Enhanced-Functionality Test Access Port and Boundary Scan Architecture</i> , Institute of Electrical and Electronic Engineers, 2009.                                                                                                 |

| 290<br>291<br>292 | [ISTO01]  | IEEE-ISTO 5001 <sup>™</sup> -2012, <i>The Nexus 5001 Forum</i> Standard for a Global Embedded <i>Processor Debug Interface</i> , version 3.0.1, IEEE- Industry Standards and Technology Organization, 2012.                                                                                               |

| 293               | [ARM01]   | ARM <sup>®</sup> CoreSight <sup>™</sup> Architecture Specification, version 2.0, ARM Limited, 2013.                                                                                                                                                                                                       |

| 294<br>295<br>296 | [AUR01]   | Aurora 8B/10B Protocol Specification, SP002 (v2.3), Xilinx, Inc., 145 <a href="http://www.xilinx.com/support/documentation/ip documentation/aurora-8b10b-protocol_spec-sp002.pdf">http://www.xilinx.com/support/documentation/ip documentation/aurora-8b10b-protocol_spec-sp002.pdf</a> , 1 October 2014. |

|            | Version 1.2 | Architecture Overview for Debug                                                                                                        |

|------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------|

|            | 13-Jul-2018 |                                                                                                                                        |

| 297<br>298 | [USB01]     | USB 3.1 Device Class Specification for Debug Device, Revision 1.0, <a href="http://www.usb.org">http://www.usb.org</a> , 14 July 2015. |

| Architecture       | Overview   | for | Debug |

|--------------------|------------|-----|-------|

| 1 II CIII CC LUI C | O VCI VICW | 101 | DCUUE |

This page intentionally left blank.

300

301

303

304

305

307

309

310 311

312 313

314

315

316

317

318

319 320

321

324

325

### 4 Debug System

#### 4.1 System Framework

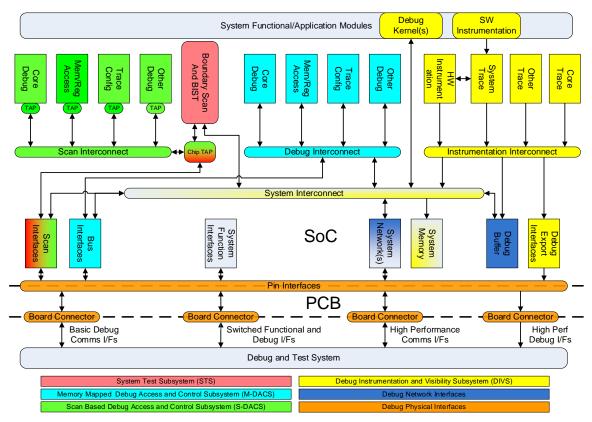

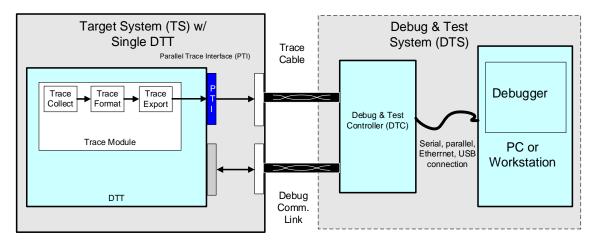

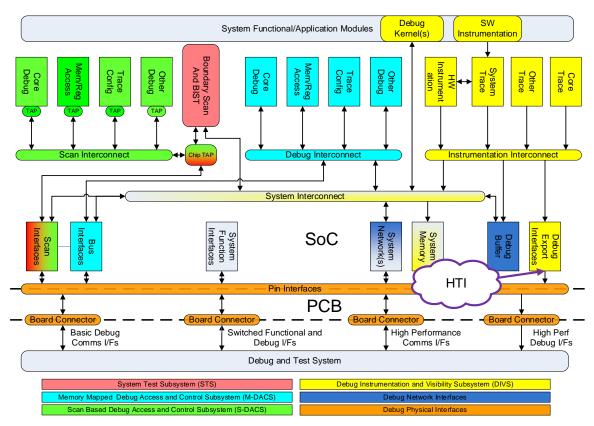

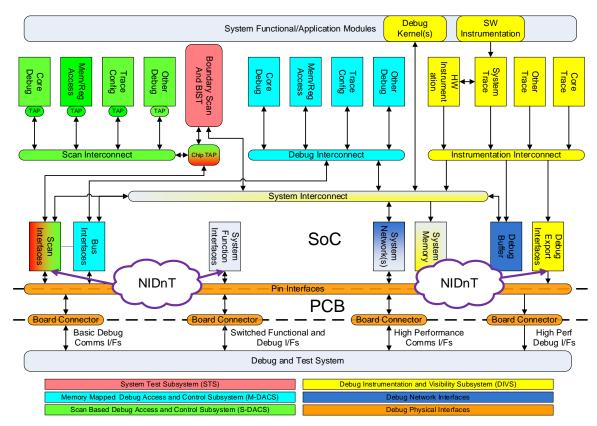

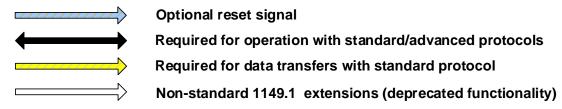

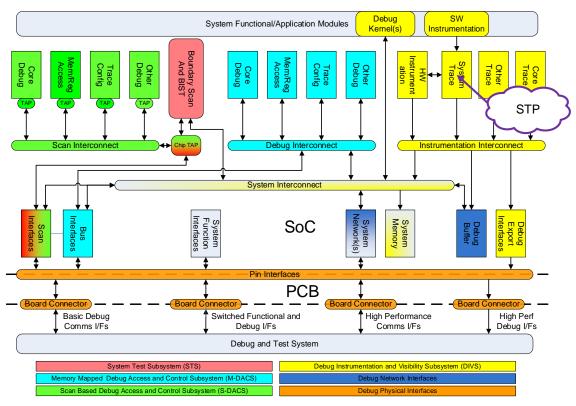

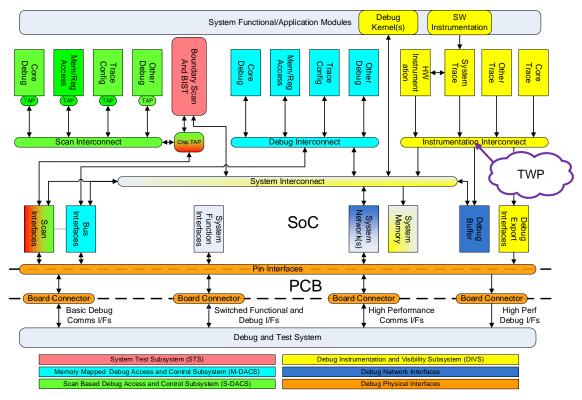

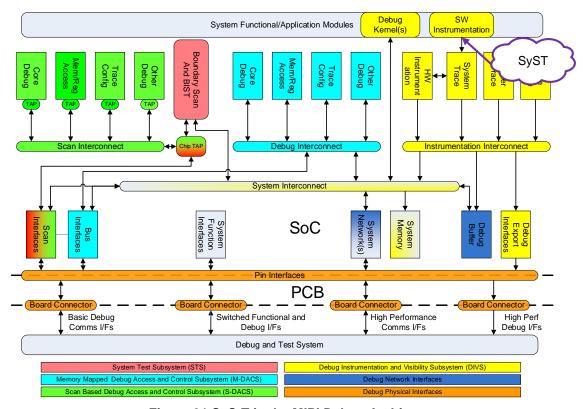

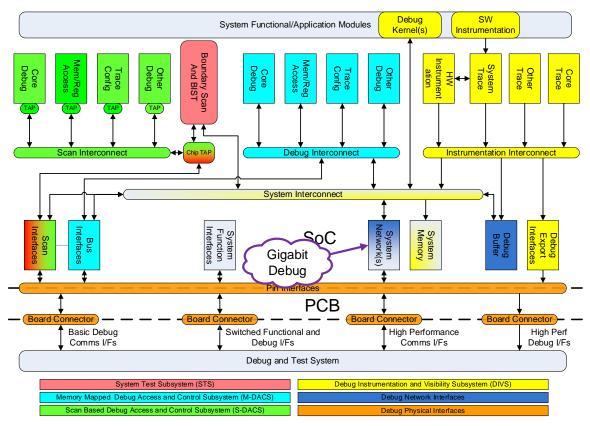

The modern systems on a chip often have complex Debug and Test architectures. In a simplistic view, the modern SoC Debug and Test architecture can be broken down into the following major subsystems:

- **Debug Access and Control Subsystem (DACS)** This subsystem provides a path for the DTS to obtain direct access to application visible system resources (registers and memory). It also provides bidirectional communication for configuration and control of debug specific modules in the TS. The communication between the debug and the DACS is generally implemented via one of the following (this is not an exhaustive list):

- Serial scan via a dedicated Debug and Test interface on the device

- Memory mapped using a dedicated debug interconnect or in some cases the application visible system interconnect

- A proprietary communication protocol and interface on the device boundary

- Debug Instrumentation and Visibility Subsystem (DIVS) This subsystem provides communication and storage of data generated by debug instrumentation modules (like processor and system trace) in the target system. DIVS communication path to the DTS is usually via high-speed serial or trace interfaces and is generally unidirectional.

- System Test Subsystem (STS) This subsystem supports communication between the DTS and the on-chip logic used for production test (boundary scan, BIST, etc.). Access to the STS is generally accomplished via serial scan.

- **Debug Physical Interfaces** (**DPI**) The physical interfaces that support debug at the SoC boundary and on the PCB.

- **Debug Network Interfaces (DNI)** The internal interfaces that allow debug and trace data to be transmitted to and from the DTS on functional networks. This communication is with dedicated intelligent resources (sometimes called the *Debug Butler*) that possibly:

- Enable *bare metal* debug on systems where the normal functional communication management is not yet functioning

- Allow debug to minimize or eliminate the use of functional resources for managing debug communications

*Figure 1* provides a top-level view of how all the pieces of the Debug and Test architecture are integrated on a device.

Figure 1 MIPI Debug Generic System Framework

326

330

331

332

333

334

335

### 4.2 The MIPI Debug and Test System

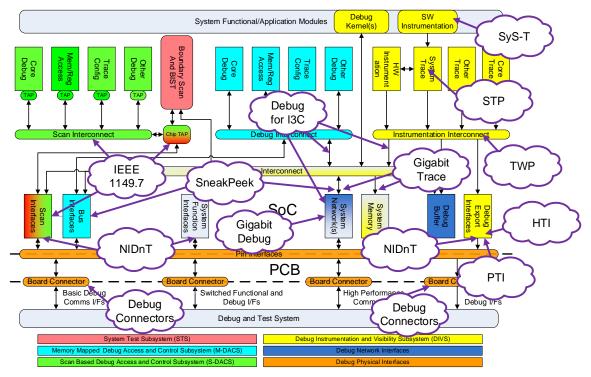

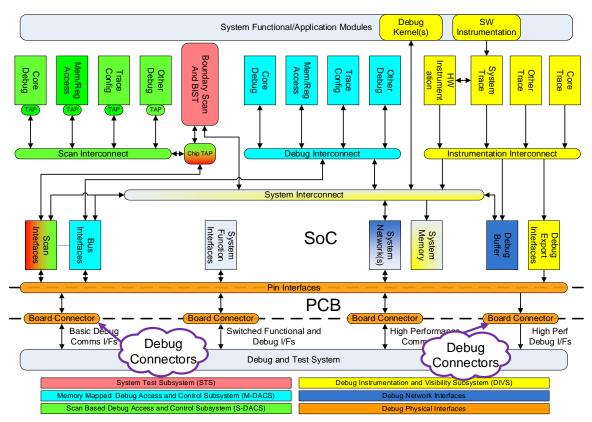

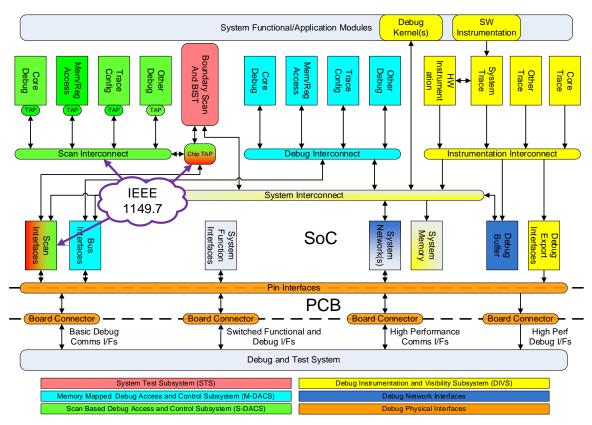

The MIPI Debug WG effort does not address all the functional blocks in the generic framework. The Debug WG standards and recommendations focus on device and board interfaces and protocols. There is also an effort to standardize on communications for debug instrumentation (i.e., trace protocols), but with a generic approach that maintains compatibility with protocols that already exist. *Figure 2* illustrates the areas of the framework that are targeted by the various MIPI Debug specifications and recommendations addressed in this document.

Figure 2 MIPI Debug Documentation and the Debug Architecture

338

339

340

341

Figure 3 shows a more detailed block diagram showing how the generic debug framework can be realized across an entire multiple-chip system. The devices share the basic debug, trace and functional interfaces. Basic run control can be provided via the shared debug connection. Trace transport can utilize a shared link dedicated to trace or a standard application visible network. In all cases, the footprint of the debug interface to the tools is greatly reduced.

Figure 3 Example MIPI System Overview

343

344

345

346

347

348

349

350

351

352353

354355

356

357358

359

360

# 5 Debug Physical Interfaces (DPI)

### 5.1 Parallel Trace Interface (PTI) Specification

#### 5.1.1 Trace and Debug Overview

It has become an accepted axiom that as the complexity of an embedded system increases, the need for system designers and developers to obtain visibility into the behavior of the system increases proportionally. One of the most common methods for providing this visibility is to provide a streaming interface on an embedded System on a Chip. This interface can be used to export data about system functionality and behavior to a host system for analysis and display. Since the data exported on this interface often allows developers to reconstruct (or "trace") some portion of system activity, these types of interface have commonly been referred to as Trace Interfaces or Trace Ports. Examples of trace data include:

- The instruction execution sequence for one or more embedded processors. This is commonly referred to as Program Counter (PC) Trace.

- Data bus transactions made by an embedded processor core. This is commonly referred to as Data Trace.

- Snapshots of transactions on the system interconnect(s). This is commonly referred to as System Trace.

- Streaming output from instrumented application code. This is commonly referred to as Instrumentation Trace.

The bandwidth requirements for the common trace functions listed above often compel system designers to implement the trace interface as a parallel interface with multiple data signals and a clock. For purposes of this document, the trace interface will subsequently be referred to as the Parallel Trace Interface or PTI.

#### 5.1.2 Relationship to MIPI Debug Architecture

*Figure 4* shows the standard MIPI debug architecture highlighting the functional areas addressed by the PTI specification.

Figure 4 PTI in the MIPI Debug Architecture

365

366

367

368

369

370

371

372

373374

375

#### 5.1.3 Trace Scenarios

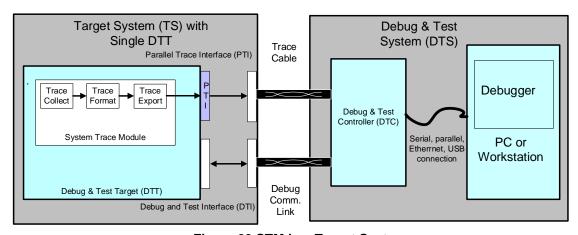

A typical embedded system may have one or more HW modules that produce trace data. The typical flow is outlined below and illustrated in *Figure 5*.

- Debug and Test Targets (DTTs) reside in the Target System (TS).

- Trace modules inside a DTT contain one or more HW sub-modules that capture the system transactions with the required data. See the Trace Collect block in *Figure 5*.

- One or more HW modules encode or compress the data into an implementation specific encoding(s). These encoding(s) are called the Trace Data Protocols (TDPs). See the Trace Format block in *Figure 5*.

- One or more HW modules export the encoded data to the DTC using device pins. The interface

used to transfer this data is the Parallel Trace Interface or PTI. See the Trace Export block in

Figure 5.

- The DTC captures the data.

- The data is decoded and analyzed using the DTS.

Figure 5 Example System with PTI

379

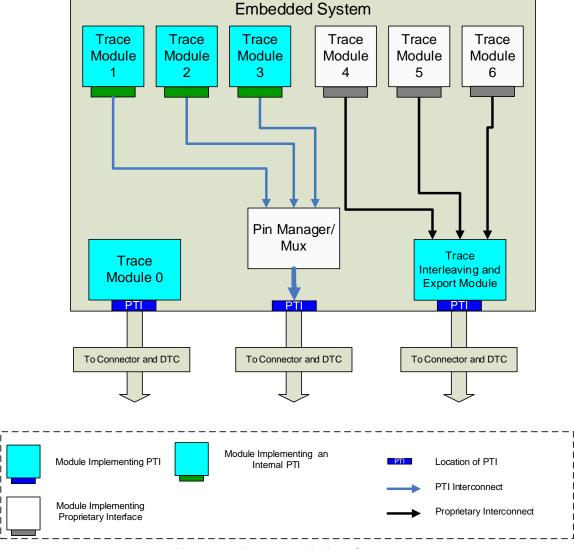

Note that only HW modules directly responsible for producing the data and clock of a PTI are required to implement a PTI. *Figure 6* shows how the PTI implementation is dependent upon system configuration.

Figure 6 PTI Layers within a System

The scenario for Trace Module 0 is reasonably straightforward. The module itself is directly connected to a dedicated PTI on the device boundary and the module is responsible for implementing the PTI.

The scenario for Trace Modules 1–3 is slightly more complex. Here multiple modules export trace through a device level pin manager or mux. This management logic is only responsible for controlling which pins on the device PTI are assigned to the device internal trace clients. It does not produce the data and clock signals for the PTI but only routes them from the various trace modules. Thus the individual trace modules are required to implement the PTI. Since the pin manager routes the internal PTI signals to the device boundary, there is also a PTI at the device pins.

The scenario for Trace Modules 4–6 shows a system where multiple trace modules provide data over a proprietary trace interconnect. This system allows data to be combined or interleaved in some fashion before export. The interleaving and export module implements the PTI and the individual trace modules communicate using implementation specific protocols that are beyond the scope of this document.

380

381

382

383

384

385

386

387

388

390

391

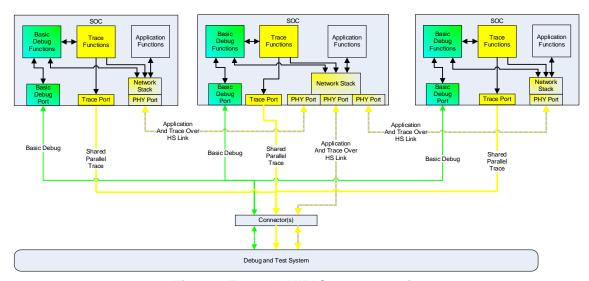

#### 5.1.3.1 Multi-Point Trace Connections

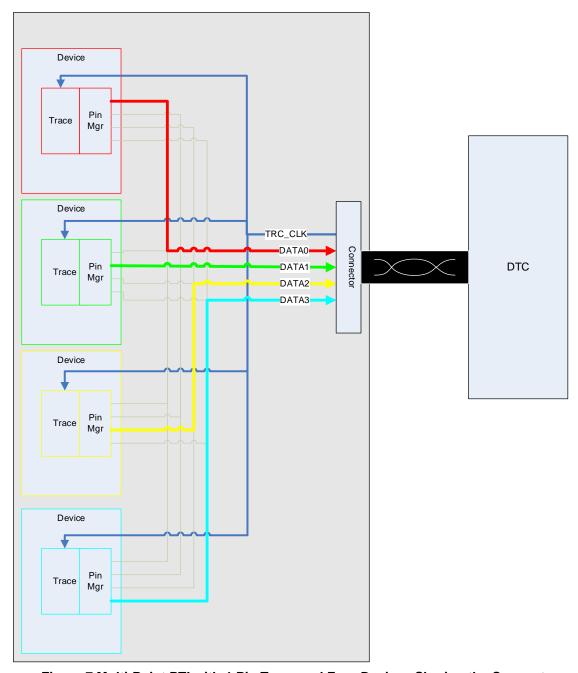

- Version 2 of the PTI specification expands the interface description to include a shared trace connection where multiple PTI interfaces are merged through a single connector on a PCB board. Multi-point PTIs are very useful for supporting trace on fielded systems that have multiple trace-enabled ASICs but only a single connector (with limited data pins) for interfacing to an external DTC. A standard example would be a mobile terminal with an application and modem SoC and a single MIPI NIDnT connection.

- Devices can be configured to drive data on a subset of the PTI signals on their boundaries. The PTI signals are merged at the connector, but only one PTI is driving any given data signal. The clock for all the interfaces is supplied from an external source (generally the DTC). *Figure 7* shows an example with four devices (each with 4-pin PTIs) sharing a connector with each of them only exporting on a single pin.

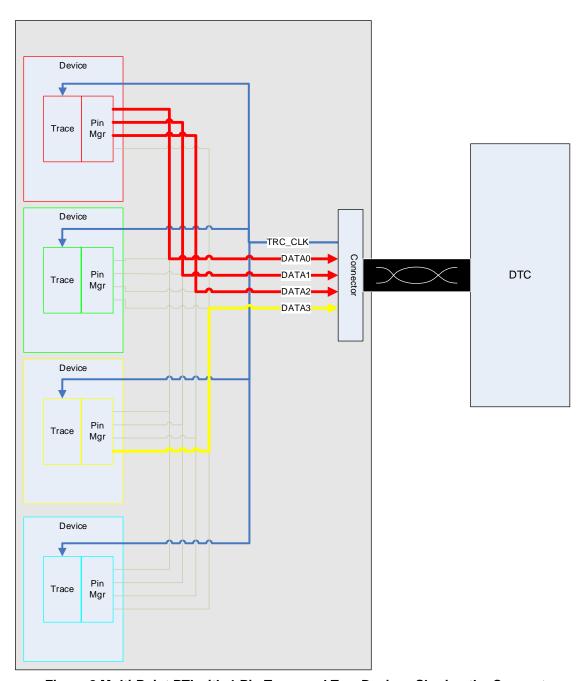

- A similar configuration is shown in *Figure 8*, but in this scenario only two devices are active and the port is shared as 3 pins and 1 pin. These are just examples, and the multi-point routing scheme defined in this document supports varying PTI widths and numbers of devices.

- Providing these enhanced features requires new operating modes for the clock and data portions of a PTI.

- Clock Modes

406

407

408

409

- PTI-out-clock Mode The PTI sources the clock along with the data

- PTI-in-clock Mode The clock for the PTI is an input to the module driving the PTI data

- Data Modes

- Point-to-point Data Mode Data indexes are fixed on the PTI

- Multi-point Data Mode Data indexes may shift across the PTI

Figure 7 Multi-Point PTI with 4-Pin Trace and Four Devices Sharing the Connector

Figure 8 Multi-Point PTI with 4-Pin Trace and Two Devices Sharing the Connector

#### 5.1.4 Detailed Specification

413

For details of the MIPI PTI, consult the document: MIPI Alliance Specification for Parallel Trace Interface, [MIPI02].

Copyright © 2014-2018 MIPI Alliance, Inc. All rights reserved.

#### 5.2 High-speed Trace Interface (HTI) Specification

#### 5.2.1 Overview

416

417

418 419

420

421

422

423

424

425

426

427

428

429

430

Transferring data off-chip from high performance embedded microprocessor cores requires a data port with sufficient trace data bandwidth. Parallel port implementations such as MIPI Parallel Trace Interface (PTI), [MIPI02], employ a clock synchronous parallel interface, using as many as 32 parallel data lines to provide the required bandwidth. Increasing CPU clock speeds and use of multiple processor cores demand increasing data port bandwidth, while at the same time the number of I/O pins used for the data port is being reduced to facilitate lower cost and a higher level of SOC/ASIC integration.

MIPI High-speed Trace Interface (HTI) is a serial implementation of the data port, taking advantage of available high-speed serial interface technology used in interfaces such as PCI Express®, DisplayPort<sup>TM</sup>, HDMI®, or USB, provides higher transmit bandwidth with fewer I/O pins compared with a parallel implementation. Unlike protocol specifications in the MIPI Gigabit Debug portfolio, such as *[MIPI08]*, HTI is not designed to be used over the high-level protocols implemented by interfaces such as PCI Express, but is intended to re-use the low-level physical high-speed portions of those interfaces, in a bare-metal environment.

#### 5.2.2 Relationship to the MIPI Debug Architecture

*Figure 9* shows the standard MIPI debug architecture highlighting the functional areas addressed by the HTI specification.

Figure 9 HTI in the MIPI Debug Architecture

#### 13-Jul-2018

#### 5.2.3 HTI Details

- HTI defines a method to transport a single stream of trace information over a channel consisting of one to

- eight high-speed serial lanes, using the Aurora 8B/10B protocol [AUR01]. HTI uses the serial simplex

- mode of Aurora to transmit data in one direction from TS to DTS.

- The HTI specification supports transmission of either the MIPI STP [MIPI03] protocol or MIPI TWP

- [MIPI04a] protocol over an HTI channel.

- The HTI specification consists of the following aspects:

- The LINK layer, which defines how the trace is packaged into the Aurora 8B/10B protocol.

- The PHY layer, which defines the electrical and clocking characteristics.

- A programmer's model for controlling HTI and providing status information.

- In addition to the trace information, the HTI LINK layer provides the ability to include:

- Optional CRC data, to assist in detecting errors in the trace transmission.

- Optional User Flow Control messages, to indicate additional information about the trace data stream.

#### 5.2.4 Detailed Specification

- For details on HTI, consult the MIPI Alliance Specification for High-speed Trace Interface (HTI),

- 446 **[MIPI09]**.

438

440

443

451

452

### **5.3 Debug Connector Recommendations**

#### 5.3.1 Dedicated Debug Connector Overview

Board developers, debug tools vendors and test tool vendors all benefit when the number of connectors and connector pin mappings used to support Debug and Test is minimized. To this end, MIPI Alliance is promoting a set of connectors and mappings that address a wide variety of debug use scenarios.

#### 5.3.2 Relationship to the MIPI Debug Architecture

*Figure 10* shows the standard MIPI debug architecture highlighting the functional areas addressed by the connector recommendation.

Figure 10 Connectors in the MIPI Debug Architecture

Version 1.2 13-Jul-2018

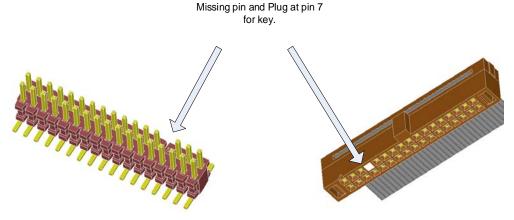

#### 5.3.3 Basic Debug Connectors

As the connector was not part of the original IEEE 1149.1 JTAG standard, a large number of different JTAG connectors have emerged. The MIPI recommendation of standard connectors promotes convergence toward a minimum set of debug connectors. The scalable 0.05 inch Samtec FTSH connector family provides a cheap, small and robust target connection and is available in many variants (including lockable ones) from multiple connector vendors. The pin-out allows scaling of the debug connection to meet different requirements. This includes very small footprint connections (down to 10 pins), legacy JTAG support (including vendor specific pins) and system level trace support (STM).

Figure 11 Basic Debug PCB (left) and Cable End Connector (34-pin Samtec FTSH)

#### 5.3.4 High-Speed Parallel Trace Connectors

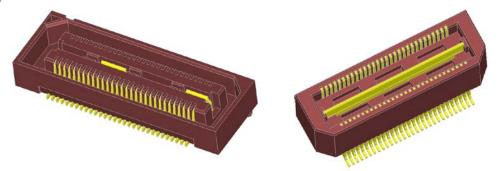

Many debug tools vendors support target systems with high-speed trace interfaces. These tools utilize a number of different mating connectors.

The MIPI Alliance Recommendation for Debug and Trace Connectors, [MIPI01], document defines two connectors for supporting high-speed trace and basic debug. The first connector is only intended for backwards-compatible designs. The second connector is recommended for new designs. The goal is to have this recommendation define a "de facto" industry standard for the trace connection and thus lessen the burden on target system and tools developers that need to support a large number of different mating connections.

The recommended trace connector is a 60 pin Samtec QSH/QTH connector. The signal to pin mapping, which is defined in the recommendation, supports one run control and several trace configurations. The different trace configurations use up to 40 data signals and up to 4 clock signals. To minimize complexity, the recommendation defines four standard configurations with one, two, three or four trace channels of varying width.

Figure 12 Recommended Samtec QSH/QTH Connector

#### 5.3.5 Detailed Documentation

For details of the MIPI recommended connectors and connector pin mappings, consult the document: MIPI Alliance Recommendation for Debug and Trace Connectors, [MIPI01].

478 479

480

481

482

483

484

485

486

487

488

489

490

#### 5.4 Narrow Interface for Debug and Test (NIDnT) Specification

#### 5.4.1 Overview

The MIPI Debug Working Group has standardized a way to utilize functional interfaces for debug or test. This technology is called NIDnT (Narrow Interface for Debug and Test). It allows better debug support in production or near-production mobile terminal units.

NIDnT technology defines low pin count, reliable, and high performance, debug interfaces that can be used in deployed mobile terminal units. These interfaces provide access to basic debug, trace of application activity, and HW test capability by reusing already existing functional interfaces. In some cases these interfaces are accessible at the packaged boundary of a mobile terminal. This technology provides the means to use functional interfaces for either functional or debug purposes. One or more functional interfaces (e.g. MMC card slot for trace and USB for basic debug) may be used to provide debug capability. NIDnT technology does not aim to replace current technologies such as debugging via a serial interface (e.g. GDB using a UART, or on-device debug agent).

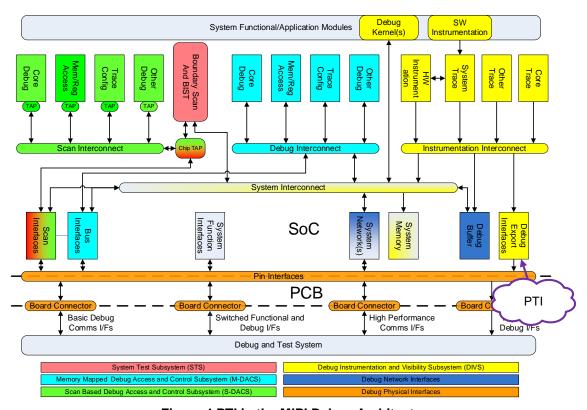

#### 5.4.2 Relationship to the MIPI Debug Architecture

*Figure 13* shows the standard MIPI debug architecture highlighting the functional areas addressed by the NIDnT specification.

Figure 13 NIDnT in the MIPI Debug Architecture

#### 5.4.3 NIDnT Details

NIDnT technology has the potential for changing the product development paradigm as it provides for the use of one or more of a mobile terminal's functional interfaces for debug. This can extend the availability of the debug capabilities used in the early stages of product development to the latter stages. This is especially valuable when these interfaces are available at the boundary of the mobile terminal's actual physical enclosure in the product's final form factor. This change in the product development paradigm is described in the following paragraphs.

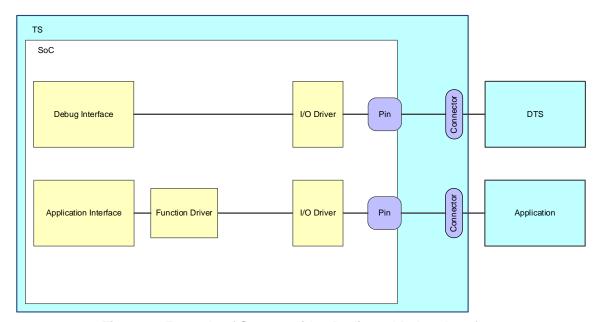

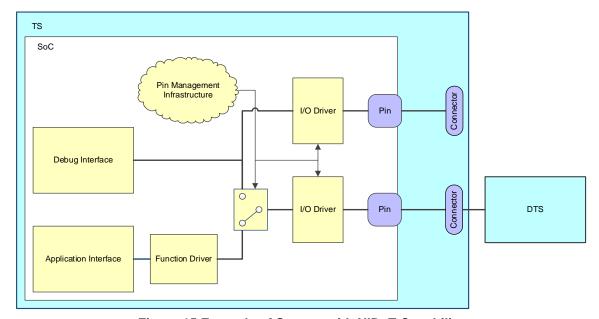

During the early stages of product development, IEEE 1149.1/1149.7/SWD/I3C based basic debug, trace of application activity, and software messages sent over simple streaming interfaces like serial ports are typically used for debug. Historically, much of this product development is performed using test or development boards. These boards provide dedicated and readily-accessible Debug and Test interfaces for connecting the tools. A system with a dedicated debug interface is shown in *Figure 14*.

Figure 14 Example of System with a Dedicated Debug Interface

In most cases, a mobile terminal product's final form factor does not have dedicated Debug and Test interfaces as these interfaces are not propagated to the boundary of the product's physical enclosure. This hampers the identification of bugs present at this point in the product development.

A mobile terminal might include a proprietary JTAG connector that requires some disassembly (e.g. removing the battery cover and battery) and the use of a test fixture. The physically invasive process of accessing this connector could itself cause bugs or RF performance issues to disappear, or new ones to appear.

Version 1.2 13-Jul-2018

Figure 15 shows how NIDnT technology extends the use of functional interfaces for Debug and Test purposes. It creates a dual use functional interface by multiplexing the debug signals with the normal function signals within the SoC in a manner that is similar to a switch. Connecting either the normal function or the debug function to the interface connects that function's inputs and outputs to the interface. Disconnecting either the normal function or debug function from the interface connects its inputs to inactive default values that create the function's inert operation while leaving its outputs unused. For example, a SoC could multiplex an IEEE 1149.7 Test Access Port (TAP) and a Parallel Trace Interface (PTI) over the functional I/Os that normally provide a microSD interface. In this case, the IEEE 1149.7 TAP could be used for both basic debugging and as a control channel for the trace function that utilizes the PTI interface.

Figure 15 Example of System with NIDnT Capability

It is expected that adapters will be used to connect a product's NIDnT Interface (e.g. microSD interface, or USB) to the MIPI Debug Connectors (as defined in [MIPI01]). The use of an adapter provides for debugging the product in its final form factor with standard debug tools, as the adapter remaps the signals presented by the tools on these standard debug connectors to the appropriate positions on the functional connectors.

## 5.4.4 Debug and Test Capabilities Supported by NIDnT Overlay Modes

A NIDnT Interface supports an operating mode that provides all functional operation of the interface (Overlay Mode 0, also called the Original Functional Mode (OFM)) and one or more non-OFM Overlay Modes (Overlay Modes 1 through n) providing debug and test capability.

The debug and test capabilities that can be supported with these Overlay Modes are listed below with their associated pin counts shown in parenthesis. These capabilities might be mixed and matched to provide one or more combinations of debug and test capability within the limitations (pin count and drive characteristics) of a specific functional interface or combination of interfaces. The combinations supported for a specific NIDnT Interface are outlined in interface-specific sections of the NIDnT specification.

## Table 1 Summary of Test/Debug Capabilities Supported by NIDnT

| Capability   | Interface with Single-Ended Electri-<br>cals                    | Interface with Differential Electricals |

|--------------|-----------------------------------------------------------------|-----------------------------------------|

|              | 2-pin (Min-Pin) Debug                                           | 4-pin High-Speed Debug                  |

| Basic Debug  | • IEEE 1149.7 <b>[IEEE02]</b>                                   | Vendor Defined Differential Debug       |

|              | Serial Wire Debug [ARM01]                                       |                                         |

|              | • UART                                                          |                                         |

|              | • I3C                                                           |                                         |

|              | Vendor Defined Single-Ended Debug                               |                                         |

|              | 5-pin Legacy Debug                                              |                                         |

|              | • IEEE 1149.1 [IEEE01]                                          |                                         |

|              | 6-pin Modified Legacy Debug                                     |                                         |

|              | Modified IEEE 1149.1 Standard with<br>return clock (deprecated) |                                         |

|              | Single-Ended Trace                                              | High-Speed Trace                        |

| Trace        | Parallel Trace Interface [MIPI02]                               | High-Speed Trace Interface (HTI)        |

| 11400        | Vendor Defined Single-Ended Trace                               | [MIPI09]                                |

|              |                                                                 | Vendor Defined Differential Trace       |

| User Defined | Vendor Defined Single-Ended                                     | Vendor Defined Differential             |

The trace function can either run with a clock shared with the 2-pin Min-Pin debug interface or run with an independent clock. If the focus is on maximum trace bandwidth, a shared clock provides the largest number of trace data pins, but ties the data rate of each data pin to the clock rate of the 2-pin Min-Pin debug interface.

Non-OFM Overlay Modes that support debug, i.e., that switch some of the NIDnT Interface pins to being used for Basic Debug signals, are called Debug Overlay Modes (see table in the NIDnT Specification, [MIPI05]).

#### 5.4.5 Functional Interfaces that are NIDnT Candidates

- The current version of the NIDnT Specification addresses the reuse of the following interface:

- 543 microSD

545

548

- USB (USB 2.0 and USB Type-C<sup>TM</sup>)

- Display (HDMI and DisplayPort (DP))

- Future versions of the NIDnT Specification might support other interfaces including, but not limited to:

- SIM (smart card)

- UniPro

#### 5.4.6 Detailed Specification

For details of NIDnT technology, consult: MIPI Alliance Specification for Narrow Interface for Debug and Test (NIDnT), [MIPI05].

# 6 Debug Access and Control Subsystem (DACS)

## 6.1 IEEE 1149.7 Debug and Test Interface Specification

- The IEEE 1149.7 standard [IEEE02] supports the needs of both Debug and Test. It is a superset of the IEEE 1149.1 standard [IEEE01] and represents a natural evolution of this standard. This approach preserves the industry's hardware and software investments in the IEEE 1149.1 standard since its inception. While this is not a MIPI specification, the min-pin debug effort started in MIPI, so it is included here to help complete the debug framework. The standard:

- Provides a substantial, yet scalable set of additional debug related capability

- Supports multiple connection topologies

- Four-wire series or star

- Two-wire star

557

558

560

575

576

- Halves the width of the interface in two-wire star configurations while maintaining performance

- Six capability classes (T0-T5) are supported, with the implementer selecting the capability class implemented. A class defines both mandatory and optional capability. Class capability increases progressively, with the capability of a class including the capability of all lower numbered classes.

- Capability classes T0-T2 support operation with the four-wire Test Access Port (TAP) (defined by the IEEE 1149.1 standard) connected in a four-wire series topology. Each of these classes incrementally extends the IEEE 1149.1 capability while using only the Standard Protocol defined by the IEEE 1149.1 standard.

- Capability classes T3 additionally supports deployment in a four-wire star topology.

- Capability classes T4-T5 provide for implementing devices with either a four-wire TAP (IEEE 1149.1 style) or a two-wire TAP (unique IEEE 1149.7 style). Devices with the four-wire TAP configuration can be operated in all connection topologies. Devices with the two-wire TAP configuration can be operated only in a two-wire scan topology.

- The T4-T5 classes incorporate the Advanced Protocol. The Advanced Protocol provides for the joint use of the TAP for real-time system instrumentation, classic debug, and test, using only the TCKC and TMSC signals as it:

- Redefines the functionality of the IEEE 1149.1 TCKC and TMSC signals

- Eliminates the need for the TDIC and TDOC signals

- Allows the use of the TAP for both scan and non-scan data transfers

- The combination of a two-wire TAP and use of the Advanced Protocol provides the capability of a fivewire IEEE 1149.1 TAP using only two signals, plus additional system debug capability.

581

582

583

584

585

586

587

588 589

590

591

592

593

594

595

596

597

598

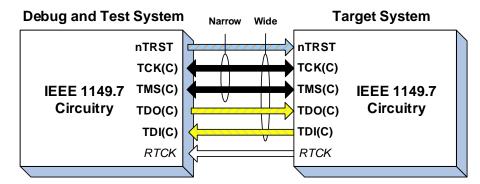

A high-level view of the IEEE 1149.7 interface connectivity between a DTS and TAPs within the TS is shown in *Figure 16*. Both the four-wire (wide) and two-wire (narrow) TAP configurations are shown with an optional test reset signal. A deprecated non-standard return clock signal is also comprehended with the four-wire configuration (the use of this and other non-standard signals is strongly discouraged by the standard).

Although TCKC is shown as bidirectional it is sourced by either the DTS or the TS

Figure 16 DTS to TS Connectivity

All capability classes begin operation using the Standard Protocol. IEEE 1149.7 operation is compatible with IEEE 1149.1 from power-up, with the function of TCK(C) and TMS(C) signals providing the functionality (or a superset thereof) of the TCK and TMS signals that is specified by the IEEE 1149.1 standard.

All IEEE 1149.7 based devices may be implemented in a manner that allows their use in system configurations where there is:

- A mix of components implementing different capability classes

- A mix of connection topologies

The DTS can use facilities defined by the standard to determine the following:

- The types of connection topologies deployed within the TS

- The component mix with the TS:

- 1149.1 components

- 1149.7 components + class of each component

600

601

602

603

## 6.1.1 Relationship to MIPI Debug Architecture

*Figure 17* shows the standard MIPI debug architecture highlighting the functional areas addressed by the IEEE 1149.7 standard.

Figure 17 IEEE 1149.7 in the MIPI Debug Architecture

### 6.1.2 Detailed Specification

For details of the 1149.7 specification, consult the document: IEEE 1149.7 Standard for Reduced-pin and Enhanced-functionality Test Access Port and Boundary Scan Architecture [IEEE02].

605

606

607

608

609

610

611

612

613

614

615

616

617

618

619 620

## 6.2 SneakPeek Specification

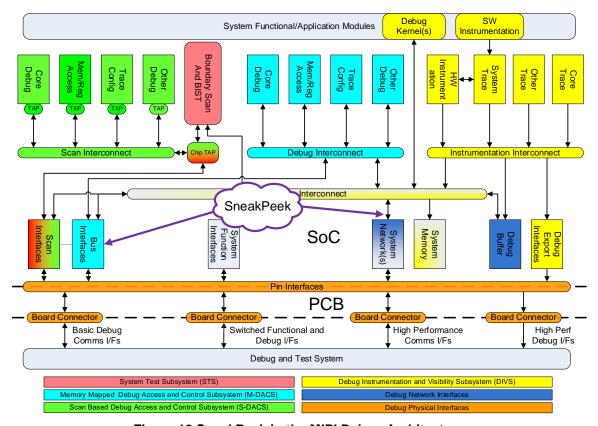

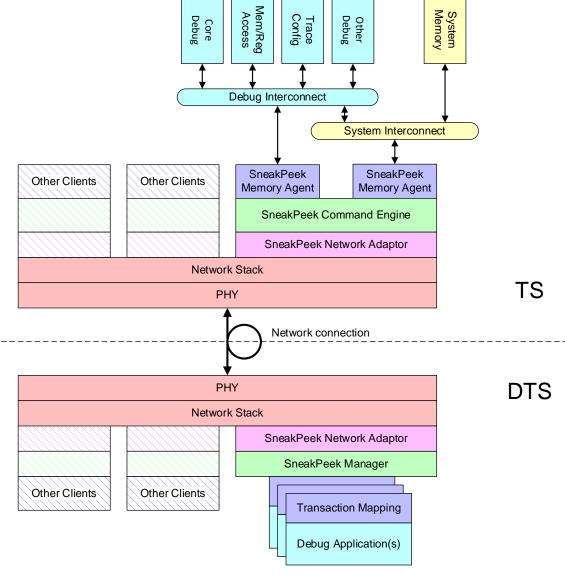

The SneakPeek framework is intended to enable debugging of a Target System via standard network connection. This is accomplished by moving a portion of the Debug and Test Controller function onto the SoC. These embedded DTC functions can be reached by network communication links that previously have not been leveraged for *DTC-like* debug. SneakPeek also leverages a significant portion of the on-chip debug infrastructure. As a result, DTC tools that previously used dedicated debug links (e.g. 1149.7 or PTI) can easily be ported to work in a SneakPeek framework through simple network adaptor layers. The identical capabilities realized via the dedicated debug interfaces should be available via SneakPeek (with possible performance penalties).

#### 6.2.1 Relationship to MIPI Debug Architecture

*Figure 18* shows the standard MIPI debug architecture highlighting the functional areas addressed by the SneakPeek specification.

Figure 18 SneakPeek in the MIPI Debug Architecture

#### 6.2.2 Overview

The SneakPeek Protocol (SPP) is used to communicate between a Debug Test System (DTS) and a mobile terminal Target System (TS). This communication facilitates using Debug Applications (typically software) within the DTS to debug the operation of the TS.

The SneakPeek Protocol abstracts the system designer from dedicated debug communication interfaces such as JTAG and replaces them with the familiar mechanism of address-mapped read and write transactions to enable the Debug Applications to observe, interrogate and adjust the Target System. These

Version 1.2 13-Jul-2018

623

625

626

627

628

629

630

631

transactions might be addressed to main system memory, special function memories, or address-mapped peripherals within the TS.

If the system requires legacy dedicated debug communication interfaces to be used internally within part of a system then these could be constructed by a dedicated address-mapped peripheral within the Target System that is then accessed by the DTS via SneakPeek.

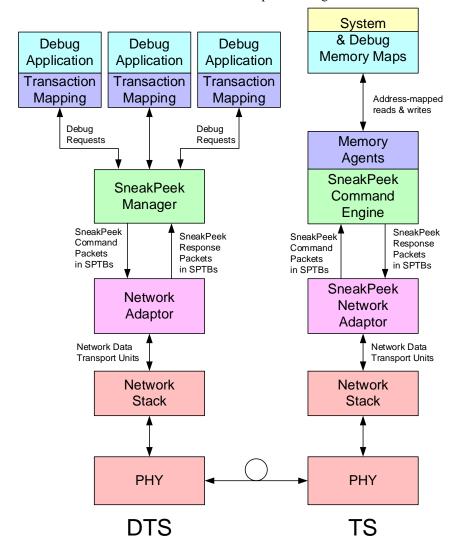

*Figure 19* illustrates the route by which one or more debug software applications in a DTS utilize SneakPeek Memory Agents within a TS to perform address-mapped transactions for them.

Figure 19 Overview of SneakPeek System

The basic communication units used by SneakPeek are SneakPeek Command Packets sent from the DTS to the TS, and SneakPeek Response Packets sent from the TS to the DTS. To provide more efficient interactions with the communication network, the DTS packs typically many Command Packets into a single SneakPeek Transfer Block (SPTB) before handing this over to the network driver for transmission to

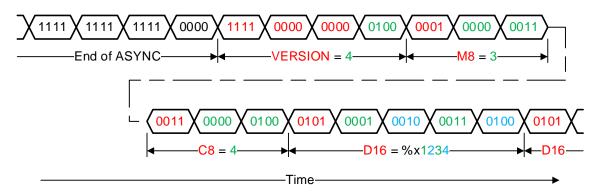

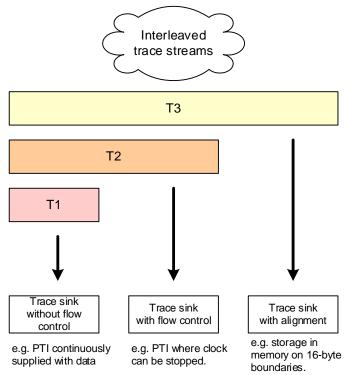

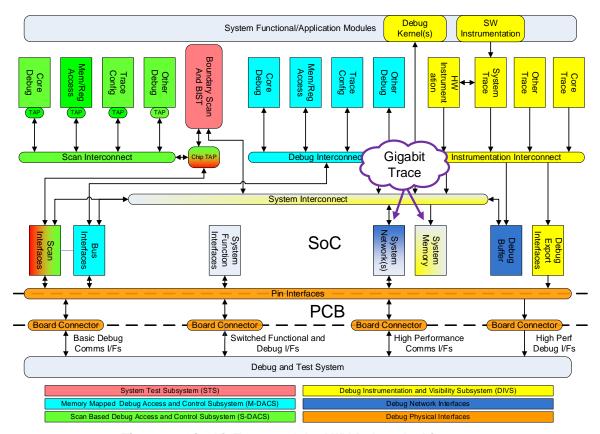

the TS. Similarly, the TS packs typically many Response Packets into a single SPTB for transmission to the DTS.