1 min read

MIPI I3C Signal Integrity Challenges on DDR5-based Server Platform Solutions

- Resources

- Conference Presentations

Azusena Lupercio Ramirez |

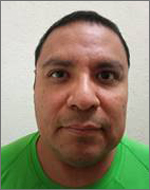

Juan Orozco |

Nestor Hernandez Cruz |

MIPI DevCon 2021

Download the presentation »

View the session »

Presented by Azusena Lupercio Ramirez, Juan Orozco and Nestor Hernandez Cruz, Intel Corporation

The MIPI I3C® protocol is first used in a server application for the DDR5 DIMM SPD function. MIPI I3C was defined for low capacitance applications, while DDR5 SPD exceeds by far the bus capacitance specification. This presentation covers the interoperability challenges of the dynamic push-pull and open-drain operating modes, on server applications with an in-depth analysis of the implications of long PCB traces, multiple DIMM routing branches, and multiple loads to the electrical and timing parameters.

Presenters

Azusena Lupercio Ramirez is a signal integrity engineer at Intel Corporation, working on Xeon-based GPIO server solutions. Azusena received a master of engineering at CINVESTAV in the research of low-power/low-voltage and PVT analysis for analog integrated circuits design.

Juan Orozco is a platform architect at Intel Corporation. Juan received his master's of engineering in electronics design at ITESO. Juan joined Intel in 2006 as a hardware designer for Xeon-based systems. He moved in 2016 to the platform architecture division, working as a platform architect for Xeon-E and Xeon-SP platforms.

Nestor Hernandez Cruz is an analog engineer with 10+ years of experience working with signal integrity, with a focus on GPIO signaling and booting interfaces. He has also collaborated in Xeon Phi, and later Xeon server generations, and contributed on the 3Dx point memory projects and their ecosystem. Nestor earned a Ph.D. in electronics and SI design for testability in 2008.