3 min read

Updates Released for Three Software Specifications: I3C HCI, DisCo for I3C and DisCo for NIDnT

![]() Matthew Schnoor, MIPI Software Working Group

:

5 June 2023

Matthew Schnoor, MIPI Software Working Group

:

5 June 2023

- News & Events

- News

- Blog

Three new updates to specifications developed by the MIPI Software Working Group have recently become available: MIPI I3C HCI℠ v1.2, MIPI DisCo℠ for I3C® v1.1 and MIPI DisCo℠ for NIDnT℠ v1.1.

MIPI I3C HCI v1.2

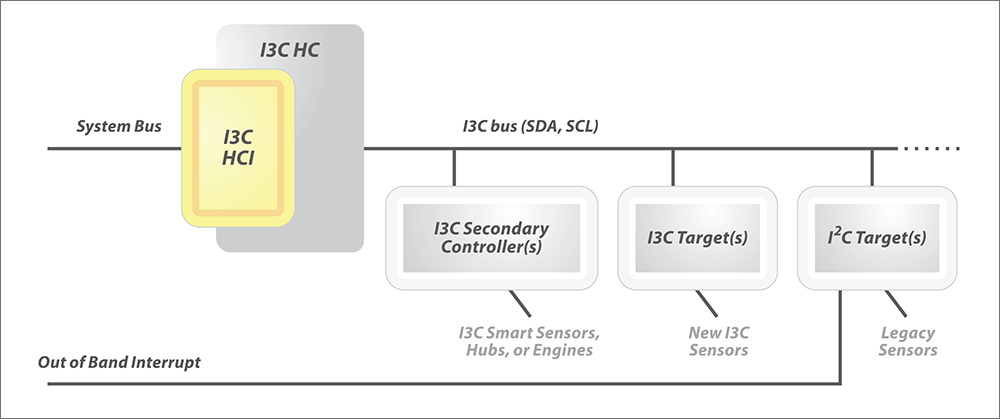

The MIPI I3C Host Controller Interface (MIPI I3C HCI) specification is intended to help designers of smartphones, computers, the Internet of Things (IoT), automotive systems and other devices to more efficiently and flexibly leverage the scalable, low-power, two-wire MIPI I3C® utility and control bus interface (as well as the MIPI I3C Basic℠ publicly available version).

With I3C HCI, designers enjoy a consistent, simplified and cost-effective method for interfacing to I3C/I3C Basic. Rather than sinking time and effort in product-specific drivers, operating-system vendors, developers and distributors can instead offer generic I3C drivers that are portable across hardware platforms, helping to keep in check costs and complexities throughout the value chain. I3C HCI is of especially clear value in that it helps vendors and developers to more easily integrate support for I3C/I3C Basic for applications that go beyond simple sensor devices.

Neither the scope nor core architectural details of I3C HCI changed with the latest specification update. The MIPI Software Working Group added new features in v1.2 to better support optional capabilities that were introduced in the latest versions of I3C and I3C Basic. Furthermore, I3C HCI v1.2 introduces a collection of “optional normative” features to address specific needs and other gaps that were identified by other MIPI Alliance working groups, member companies and liaison partners. These features include:

- Dead bus recovery

- Standby controller

- Simple and more flexible scheduled transfer commands

- Early termination of High Data Rate (HDR) data transfer

- Streaming in-band interrupts (IBIs) with no defined end of payload data

- IBI credit counters

Some of the new features are widely applicable across I3C/I3C Basic use cases, while others are driven by more niche applications.

Dead bus recovery, for example, enables a designer to use a probe to determine whether an I3C/I3C Basic bus has already been configured and, if so, whether an active controller is in charge of that bus or the host can assume control. The introduction of support for standby controller enables control to automatically be passed from one controller device to another (and then go into standby while waiting to be reactivated). Functionality for IBI credit counters is designed to give the host better control of incoming data payloads, and contributes to more efficient automated management and usage of memory per target in a use case.

These new I3C HCI features are especially valuable in use cases where there is the potential for multiple controllers on an I3C/I3C Basic bus. A laptop application, with its high number of sensors and high sensitivity to power usage, would be a prime example. In this way, v1.2 makes I3C/I3C Basic an even more valuable specification for applications beyond mobile devices.

In addition, with v1.2 of I3C HCI, normative definitions for handling of transfer command and response have been removed. A separate specification—MIPI I3C Transfer Command Response Interface (MIPI I3C TCRI℠)—was released in 2022 to define these standard structures that I3C/I3C Basic controller implementations can use as part of an interface for any application (see “New MIPI Specification Standardizes Transfer Command and Response Across I3C/I3C Basic Implementations”).

MIPI DisCo for I3C v1.1 and DisCo for NIDnT v1.1

The MIPI Software Working Group also has recently revised two other specifications: MIPI DisCo for I3C and MIPI DisCo for Narrow Interface for Debug and Test (MIPI DisCo for NIDnT). Both leverage the base MIPI Discovery and Configuration (MIPI DisCo) software framework to allow major operating systems to identify MIPI-conformant external devices in systems and automatically implement drivers for them. In such ways, the DisCo specifications aid integration of sensor devices with little or no requirement for development of application-specific drivers. The goal again is for system designers to be able to roll out product innovations for any application space more quickly and at lower cost.

DisCo for I3C v1.1 introduces support for describing multiple virtual targets on the I3C bus, as well as for defining the maximum speed of the bus based on what the particular targets in use can accommodate. These new capabilities expand the specification’s relevance in use cases employing more complicated buses with more complicated targets, and they ultimately render system development based on I3C/I3C Basic to be more self-intuitive.

DisCo for NIDnT v1.1 revises the specification to align with the most recent changes introduced in MIPI NIDnT v1.2.1. The NIDnT specification defines a standardized way to use functional ports on a device for debug and test procedures.

Both DisCo for I3C v1.1 and DisCo for NIDnT v1.1 also include revisions to replace objectionable terms with ones that more accurately reflect the functions of technical devices.

Accessing and Shaping the Specifications

All three specifications are publicly available for download by developers and the open-source community, in addition to MIPI members.

As always, we welcome your contributions to the ongoing work of the MIPI Software Working Group. Please contact us at software@mipi.org.

Matthew Schnoor is a debug architect at Intel and has more than two decades of experience in various Intel business groups. With the MIPI Alliance, Matthew has primarily focused on software development, silicon validation and system debug architecture. He is a former chair of the MIPI Software Working Group and also works across and within several other MIPI groups to support development within the MIPI I3C ecosystem.