2 min read

New MIPI I/O Bridges Working Group – A Conversation with Chair Aruni Nelson

![]() Sharmion Kerley, MIPI Director of Marketing and Membership

:

3 September 2025

Sharmion Kerley, MIPI Director of Marketing and Membership

:

3 September 2025

- News & Events

- News

- Blog

Earlier this year, MIPI established the I/O Bridges Working Group, which was promoted from a 2024 MIPI Birds of a Feather (BoF) group, to explore the need for standardized hardware and software solutions to support I/O bridge use cases in computing segments.

We sat down with Aruni Nelson, I/O Bridges Working Group chair, to learn more about the new group and its near-term plans for the development of I/O bridge specifications.

Q: For context, what is an I/O bridge?

An I/O (Input/Output) bridge is a device that exposes one or more native I/O protocols/interfaces over a single I/O link. This bridge acts as a translator, aggregator and manager of data and control signals between a host system and multiple I/O interfaces. This allows the host system to communicate with multiple devices using various protocols over a single I/O link and allows the host system to offload the management of the bridged I/O interfaces.

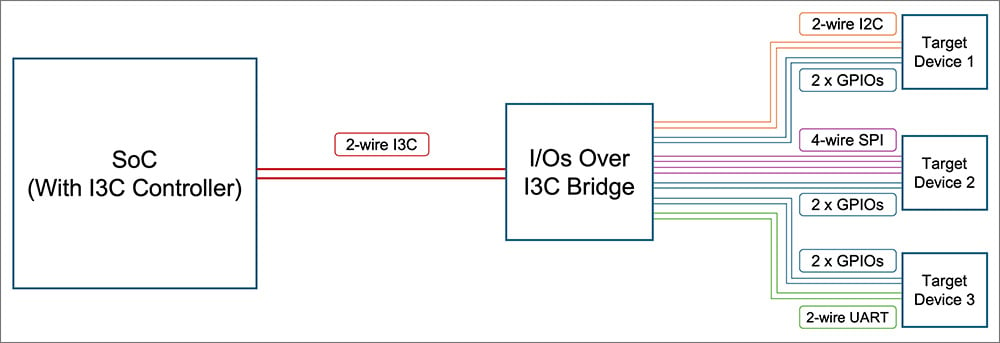

For example, an I3C bridge can enable an I3C controller in a host system to access multiple I2C buses and devices without the controller having native multi-bus I2C support. Similarly, bridging SPI, UART and GPIO over I3C can reduce system pin count, simplify printed circuit board (PCB) routing, lower power consumption and consolidate device management into a single high-performance interconnect.

By multiplexing multiple I/O protocols over one physical I/O bus, the bridge can significantly reduce the number of physical pins required on systems on chips (SoCs), streamline system design and extend the life of existing legacy peripherals without re-design.

Example Use of an I/O Bridge

Q: What is the market need for I/O bridges?

The rapid expansion of IoT, embedded systems and connected devices has created a strong need for standardized, efficient ways to connect legacy peripherals with modern, high-performance interconnects. Many computing platforms still rely on multiple I2C, SPI, UART and GPIO interfaces, yet system designers are under pressure to reduce pin count, lower power consumption and simplify PCB layouts.

Currently system designers are reliant on proprietary solutions to convert one or more I/O protocols to another I/O protocol, requiring custom hardware and software that limits scalability, interoperability and long-term support. Standardized bridge solutions can facilitate interoperability, scalability and adoption of fast-moving technologies.

Q: Can you tell us more about the working group’s charter and initial areas of focus?

At a high level, the group is focused on developing a standardized framework for bridging multiple legacy and modern I/O protocols over a single I/O interface of choice. Our three primary objectives are:

- I/O bridging at logical and protocol layer

- Design, detection, enumeration, configuration and management of the I/O bridges and the bridged devices connected to the I/O bridges

- Software and hardware definitions for standard I/O bridges to ensure robust and interoperable implementations

Our initial focus is on the creation of a new I/Os Over MIPI I3C Bridge Specification for bridging legacy I2C, SPI, UART and GPIOs over MIPI I3C®, plus related technical supporting documents. We plan to cover electrical considerations of I/O interfaces, I/O bridge detection, use of associated software, capabilities discovery, configuration and management, end-to-end operational flows and implementation recommendations based on use cases.

The working group’s charter is intentionally broad to accommodate future MIPI bridging specifications, ensuring the framework remains scalable for different interconnects and system requirements.

Q: Which MIPI working groups are collaborating to develop the I3C bridge specification?

We are collaborating with the I3C Working Group and the I3C Basic Ad Hoc Working Group (for I3C and I3C Basic™, respectively), as well as the Software Working Group, which developed the MIPI I3C Host Controller Interface (MIPI I3C HCITM) and the MIPI I3C Transfer Command Response Interface (MIPI I3C TCRITM) specifications. We expect to work with other groups as other potential bridging specifications are explored.

Q: How do I get involved?

The I/O Bridges Working Group, open to MIPI Contributor members, currently meets weekly via teleconference. Participants who cannot attend the meetings may still subscribe to the group's activities via the Causeway member portal and contribute to discussions through email.